# 새로운 구조의 프로그램어블 주파수 분주기를 사용한 주파수 합성기 설계

정회원 김 태 엽\*, 박 수 양\*\*, 손 상 희\*\*\*

## Design of Frequency Synthesizer using Novel Architecture Programmable Frequency Divider

Tae-Yob Kim, Soo-Yang Park, and Sang-Hee Son Regular Members

요 약

본 논문에서는 50%의 duty cycle 출력을 가지며, 디지털 방식으로 분주수를 제어할 수 있는 새로운 분주기 구조를 제안하였다. 그리고 0.25㎞ 2-poly, 5-metal CMOS 공정 파라미터를 이용한 HSPICE 모의실험을 통해서 제안한 주파수 분주기를 이용한 900㎞ 주파수 합성기를 설계하였다. 제안한 주파수 분주기의 동작은 0.65㎞ 2-poly, 2-metal CMOS 공정을 사용하여 제작한 칩을 측정하여 확인하였다. 설계한 전압제어발진기(VCO)는 2.5V 전원전압 하에서 900㎞의 중간주파수, ±10%의 동작 범위, 154㎞V의 이득을 가진다. 또한 모의실험 결과 주파수 합성기의 settling time은 약 1.5㎞이고, 짝수와 흘수 분주시 50%의 duty cycle과 820㎞ 1億㎞의 동작 주파수 범위를 갖으며, 전력소모는 대략 70㎜임을 확인하였다.

#### **ABSTRACT**

In this paper, a novel architecture of programmable divider with fifty percent duty cycle output and programmable dividing number has been proposed. Through HSPICE simulation, a 900M½ frequency synthesizer with proposed frequency divider has designed in a standard  $0.25\mu$ m CMOS technology. To verify the operation of proposed frequency divider, a chip had been fabricated using  $0.65\mu$ m 2-poly, 3-metal standard CMOS processing and experimental result shows that the proposed frequency divider works well. The designed voltage controlled oscillator(VCO) has a center frequency of 900M½, a tuning range of  $\pm 10\%$ , and a gain of 154M½V. The simulated frequency synthesizer performance has a settling time of  $1.5\mu$ s, a frequency range from 820M½ to 10% and power consumption of  $70\,$ mW at 2.5V power supply voltage.

#### I . 서 론

이동 통신 시장의 지속적인 성장에 따라 전력소 모가 작고 크기가 작은 무선 통신용 부품에 대한 연구가 활발히 이루어지고 있으며, 그 중에서도 고 성능 주파수 합성기는 핵심적인 구성블록 중의 하 나이다<sup>[1]</sup>. 일반적으로 이동 통신용 주파수 합성기는 PLL(Phase Locked Loop)을 사용하며, 이 PLL 주 파수 합성기를 구성하기 위해서는 VCO, prescaler 및 주파수 분주기와 같은 고주파 부품이 필요하다 [1,3,6]. 기존에는 주파수 합성기가 GaAs나 바이폴라 기술로 구현된 고주파 부품과 CMOS 공정기술로 구현된 저주파 부품으로 구현되었지만 최근에는 CMOS 공정기술의 발달로 CMOS 공정기술을 이용한 고주파 부품 회로설계가 가능하게 되었고, 점차

<sup>\*</sup>청주대학교 이공대학 전자공학과

<sup>\*\*</sup>세빛아이에스(주) 이미지센서설계 연구소

<sup>\*\*\*</sup>청주대학교 이공대학 정보통신공학부

논문번호: K01156-0702, 접수일자: 2001년 7월 2일

<sup>※</sup> 본 연구는 과학기술부、한국과학재단 지정 청주대학교 정보통신연구센터의 지원에 의한 것입니다

<sup>※</sup> 본 연구는 반도체설계교육센터(IDEC)의 부분적인 지원을 받아 이루어졌음

one-chip 화되어 가는 추세이다. 따라서 CMOS 공 정을 이용한 PLL 주파수 합성기 설계에 대한 연구 가 많이 시도되고 있다<sup>7.8</sup>.

최근에는 CMOS 주파수 합성기 설계에 있어서 성능항상을 위한 여러 가지 시도가 이루어지고 있 다. 이것은 잡음 특성이 우수한 VCO 연구, 저전력 및 소형화를 위한 주파수 분주기, PFD, prescaler 구성 회로의 고성능 및 단순화를 위한 연구 등으로 이어지고 있다.

본 논문에서는 기존의 방식에 비해 상대적으로 회로의 구성이 용이하고 넓은 프로그램 주파수 범위를 갖는 새로운 구조의 주파수 분주기와 1GHz VCO, positive edge-triggerd D 플립플롭을 이용한 PFD 등을 사용하여 주파수 합성기를 설계하였다. 설계 및 동작검증은 0.25 μm 표준 CMOS 공정 파라미터와 HSPICE를 이용하였다. 또한 제안한 주파수분주기의 동작은 0.65 μm 표준 CMOS 공정으로 제작한 칩을 측정하여 동작을 확인하였으며, 본 주파수합성기 설계에는 동일한 구조의 주파수분주기 사용하였다.

## Ⅱ. 주파수 합성기 설계

#### 가. 구조

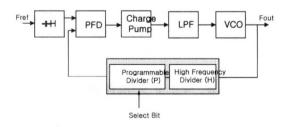

설계한 주파수 합성기는 VCO, 루프필터, 프로그래머블 N-분주기, 고주파 분주기, charge pump, PFD등으로 구성되었으며, 구조는 그림 1과 같다. 고주파 및 저주파 부품을 one-chip화한 주파수 합성기를 만들기 위해서는 각 기능블록의 잡음 특성, 회로의 단순화 및 소형화가 가장 주된 관심사라 할수 있다.

그림 1. 설계한 주파수 합성기 블록도

본 논문에서는 새로운 구조의 프로그램 가능한 주파수 분주기에 대한 동작설명과 측정결과, 전원 잡음에 둔감한 VCO의 설계 방법, 그리고 이들을 이용한 주파수 합성기의 설계에 대해서 논한다.

#### 나, 주파수 분주기 설계

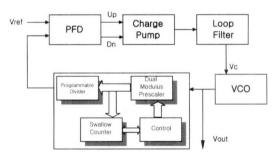

그림 2와 같은 기존의 주파수 합성기에서는 높은 주파수의 VCO의 출력을 분주하기 위해서 dualmodulus prescaler, swallow 카우터, 프로그래머블 분주기 등을 사용한다<sup>[1,6]</sup>. 이들은 구조가 복잡한 반 면에 분주할 수 있는 범위가 한정적인 단점이 있다. 예를 들어 32/33 분주시 dual-modulus prescaler를 사용할 경우에는 1024 이하의 프로그램 값은 분주 할 수 없게 된다. 그러나 제안한 주파수 분주기를 이용하면 원하는 짝수 및 홀수 분주를 얻을 수 있 다. 그림 3은 제안한 주파수 분주기의 블록도이다. 이 분주기는 그림 2의 점선으로 표시된 블록에서 수행하는 기능을 그림 1에 있는 고주파 분주기와 함께 사용하면 간단하게 구현할 수 있다. 그림 1의 고주파 분주기는 제안한 주파수 분주기의 입력주파 수 범위가 500배요 이기 때문에 더 높은 주파수의 VCO 출력 주파수를 입력주파수 범위에 들어가도록 하기 위해서 사용하였다. 그러나 이 고주파분주기를 사용하면 주파수 합성기의 출력주파수에 영향을 주 게 되는데 이 문제는 PFD의 앞단에 고주파분주기 와 동일한 분주수의 분주기를 사용하면 서로 상쇄 될 수 있다.

그림 2. Dual-modulus prescaler를 사용한 기존의 주파수 합성기 블록도

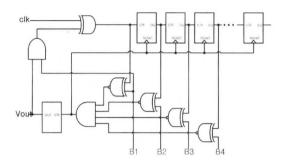

그림 3에 있는 제안한 분주기 회로의 동작은 각각의 flip-flop 입력에 들어가는 clk 신호와 프로그램값(B1, B2, B3, B4의 설정값)이 각각의 EX-NOR gate의 입력으로 인가된다. 여기에서 프로그램값은 "분주수 +1"의 binary 값으로 프로그램 해준다. 예를 들어 그림 2와 같이 6분주의 분주수를 얻기 위해서는 6의 binary 값인 "0101"이 아니라 "0110"을 프로그램 해주면 된다. 그 이유는 B1, B2, B3, B4에 저장되어 있는 프로그램 값은 "0110" 이므로 7의 binary 값이 입력되는 순간 최종 출력단에 있는

flip-flop이 초기화되기 때문이다. 이것은 짝수 및 홀수 분주에 대해서도 동일하게 적용된다.

그림 3. 제안한 프로그램어블 주파수 분주기 회로도

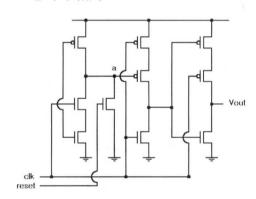

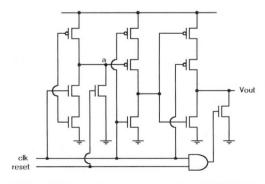

그림 4는 negative edge-triggered TSPC-TFF<sup>[10]</sup>으로 high 상태일 때 reset되도록 설계한 것이다. 또한 그림 3의 상단에 위치한 flip-flop 중 맨 처음에 사용한 flip-flop은 clk 입력이 high인 상태에서도 reset이 high 상태이면 출력전압이 low가 되도록 하기 위해서 그림 5와 같이 AND gate와 출력단에 NMOS를 추가하였다.

그림 4. Negative-edge triggered TSPC-TFF

그림 5. 변형된 형태의 negative-edge triggered TSPC-TFF

제안된 주파수 분주기를 10bit(B1~B10)으로 구성 하면 최대 입력주파수를 2분주~2<sup>10</sup> 분주까지 모든 분주수를 얻을 수 있다.

#### 다. 전압제어발진기(VCO) 설계

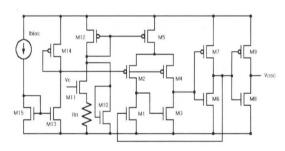

전원 잡음에 의한 영향을 최소화하기 위해서 본 논문에서는 pseudo NMOS inverter를 사용하였다. pseudo NMOS inverter의 게이트 바이어스 전압은 전원전압의 변화에 따라서 변하는 전압원으로 이루어졌다. 그림 6은 설계한 전압제어발진기의 회로도이며, 동작원리는 다음과 같다. 먼저 M2, M4는 선형영역에서 동작하고 M1, M2는 이를 구동하고 있는 pseudo NMOS 형태의 delay cell을 구성한다. 여기에서 M2, M4의 게이트 전압은 M13, M14의 드레인 전압에 의해 바이어스 되며 전원 잡음에 의해 전원전압이 높아지면 M2, M4의 게이트와 소스전압차가 작아지며 이로 인해 선형영역에서 동작하는 M2, M4의 트랜스컨덕턴스가 감소한다. 이로 인해 delay cell의 시정수가 증가하게 되고 전압제어 발진기의 출력주파수는 일정하게 유지될 수 있다.

그림 6. 설계한 전압제어 발진기 회로도

#### 라. 기타 회로 설계

설계한 PFD는 두 개의 positive edge-triggered D flip-flop을 사용하여 설계하였다<sup>19</sup>. charge pump는 차동구조로 설계하였으며, loop filter는 간단한 2차루프필터를 사용하였다.

#### Ⅲ. 측정 및 모의실험 결과

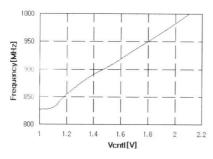

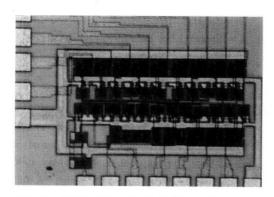

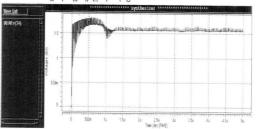

그림 7은 설계한 전압제어발진기의 Ventl 전압에 대한 출력 주파수의 변화를 모의실험한 결과이며, 900㎞의 중간주파수, ±10%의 동작 범위, 154㎞/V의 이득을 가진다. 그림 8은 0.65㎞ 2-poly, 2-metal CMOS 공정으로 제작한 주파수 분주기의 현미경 사진이며, 50% duty cycle을 확인할 수 있다. 그림 9, 그림 10은 각각 10㎞ 입력에 대해서 6분주와 7

분주한 파형을 오실로스코프로 측정한 것이며, HP8110A 펄스발생기와 TDS3052 오실로스코프를 사용하여 측정하였다.

그림 11, 12는 83.3세b 입력주파수를 10분주했을 경우, 그림 13, 14는 100세b 입력 주파수를 9분주 했을 경우에 대한 주파수 합성기의 전달특성과 입 출력을 모의실험 한 결과로서, 83.3세b와 100세b의 입력 주파수를 10분주와 9분주한 결과 정확히 833 Mb와 900세b의 출력 주파수를 얻을 수 있었으며,

그림 7. 전압제어 발진기의 Vcntl 에 대한 출력주파수 모 의 실험 결과

그림 8. 제작한 새로운 구조의 주파수 분주기의 현미경 사진

그림 9. 10Mb의 입력 주파수가 가해진 경우의 6분주 측정 결과

2.5V 전원 전압에서 settling time은 약 1.5 $\mu$ s, 전력 소모는 대략 70째, 820Mb~16b 의 동작 주파수 범 위를 가짐을 알 수 있었다.

그림 10. 10Mb의 입력 주파수가 가해진 경우의 7분주 측정 결과

그림 11. 입력 주파수가 83.3Mb일 때 주파수 합성기 단위 응답

그림 12. 입력 주파수가 83.3Mb일 때 10분주한 주파수 합 성기 입력/출력 측성

그림 13. 입력 주파수가 100Mb 일 때 9분주한 주파수 합 성기 전달 특성

그림 14. 입력 주파수가 100Mb일 때 9분주한 주파수 합성 기 입력/출력 특성

표 1은 설계한 주파수 분주기와 주파수 합성기의 측정 및 모의실험 결과를 정리한 것이다.

표 1. 주파수 분주기와 주파수 합성기의 시뮬레이션 결과와 측정 결과

|                   | Frequency<br>Divider |                 | Frequency<br>Synthesizer |

|-------------------|----------------------|-----------------|--------------------------|

|                   | Simulation           | Measurement     | Simulation               |

| Frequency         | 200MHz               | 10MHz           | 0.82~1GHz                |

| Power consumption | 15 mW                | 13mW            | 70nW                     |

| Duty cycle        | 50%                  | 50%             | 50%                      |

| Supply Voltage    | 3V                   | 3V              | 2.5V                     |

| Technology        | 0.65μm<br>CMOS       | 0.65 μm<br>CMOS | $0.25\mu\mathrm{m}$ CMOS |

## Ⅳ. 결론

본 논문에서는 원하는 홀수, 짝수 분주수를 구현 할 수 있는 새로운 구조의 주파수 분주기와 전원 잡음에 둔감한 전압제어 발진기를 이용하여 1GHz 주파수 합성기를 설계하였다. 회로는 0.25μm 2-poly, 5-metal CMOS 공정 파라미터를 사용하여 HSPICE 모의실험을 통해 설계하였다. 또한 새로운 구조의 주파수 분주기 동작은 0.65 μm 2-poly, 2-metal CMOS 공정으로 제작하여 측정을 통해 확인하였다. 측정 결과는 모의실험 결과와 같이 짝수와 홀수 분 주시 50%의 duty cycle을 구현할 수 있었다. 모의 실험의 경우 주파수 분주기는 200Mb의 입력 주파수 를 분주할 수 있었지만 실제 칩 측정은 20Mbr가지의 입력 주파수만 분주가 가능했는데 이것은 고주파 출력버퍼의 설계 및 평가보드 제작상의 문제점 때 문인 것으로 판단된다. 따라서 여기에서 설계한 주 파수 합성기는 측정을 고려하여 수십 Mb 대역으로 출력주파수를 떨어뜨릴 수 있도록 전압제어발진기의 출력단에 적절한 분주수의 주파수 분주기 및 버퍼 를 사용하였고 출력 버퍼의 설계 또한 부하용량을 충분히 고려하여 설계하였다.

#### 참고문헌

- [1] Seog-Jun Lee, Beomsup Kim, Kwyro Lee, "A Fully Integrated Low-Noise 1-0½ Frequency Synthesizer Design for Mobile Communication Application" IEEE Journal of Solid-State Circuits, Vol.32, No.5, May 1997

- [2] Hamid R. Rate, Hirad Samavati, and Thomas H. Lee, "A 50Hz, 32mW CMOS Frequency Synthesizer With an Injection Locked Frequency Divider" 1999 Symposium on VLSI Circuits Digest of Technical Papers

- [3] Behzad Razavi, "Challenges in the Design of Frequency Synthesizers for Wireless Applications" IEEE 1997 Custom Integrated Circuits Conference

- [4] Behzad Razavi " RF MICROELECTRONICS" Prentice-Hall, Upper Saddle River, NJ 07458

- [5] Christopher Lam, Behzad Razavi, "A 2.66H/5.2 6Hz Frequency Synthesizer in 0.4-\(\mu\mathrm{m}\) CMOS Technology," 1999 symposium on VLSI Circuit Digest of Technical Papers

- [6] Patrik Larsson "High-Speed Architecture for a Programmable Frequency Divider and a Dual-Modulus Prescaler." IEEE Journal of Solid-State Circuits, Vol.31, No.5, May 1996

- [7] M.Soyuer, J.F.Ewen, and H.L.Chuang, "A fully monolithic 1.25GHz CMOS frequency synthesizer," in Symp. VLSI Circuits Dig. Tech. Papers, June 1994, pp.127-128

- [8] M.Thamsirianunt and T.A.Kwasniewski, "A 1.2

µm CMOS implementation of a low-power 900

Mlz mobile radio frequency synthesizer ," in

CICC Dig. Tech. Papers, May 1994,

pp.16.2.1-16.2.4.

- [9] Won-Hyo Lee, Sun-Dae Lee, and Jun-Dong Cho, "A high-speed, low-power phase frequency detector and charge-pump circuits for high frequency phase-locked-loop," IEICE Trans Fundamentals of Engineering, 1994

- [10] Byungsoo Chang, Joonbae Park, and Wonchan

Kim, "A 1.2GHz CMOS dual-modulus prescaler using new dynamic D-type flip-flops," IEEE Journal of Solid-State Circuits, Vol. 31, No.5, May 1996

#### 김 태 엽(Tae-Yob Kim)

1999년 2월 : 청주대학교 반도체 공학과 학사 2001년 2월 : 청주대학교 전자공 학과 석사

2002년 2월 ~ 현재 : Sys On

Chip 대리

<주관심 분야> Analog Chip 설계, Bluetooth

#### 박 수 양(Soo-Yang Park)

1998년 2월 : 청주대학교 반도체 공학과 학사

2000년 2월 : 청주대학교 전자공 학과 석사

2002년 현재 : 실리콘 웍스 주임

연구원

<주관심 분야> Analog Mixed Mode Circuit Design

#### 손 상 희(Sang-Hee Son)

1988년 8월 : 한양대학교 전자공 학 박사

1988년 9월~1991년 2월 : 순천 향대학교 전산학과 전임 강사

1991년 3월~ 현재 : 청주대학교 정보통신 공학부 교수

<주관심 분야> 고주파 아날로그 CMOS회로 설계, CMOS Image Sensor Syterm 설계