# 체배기 이론을 이용한 Ka-대역 고조파 믹서 설계

정회원 고 민 호\*, 강 석 엽\*, 종신회원 박 효 달\*

# A Ka-band Harmonic Mixer Design Using Multiplier Theory

Min-Ho Go\*, Suk-Youb Kang\* Regular Members, Hyo-Dal Park\* Lifelong Members

요 약

본 논문에서는 주파수 채배기 이론에 근거하여 단일 능동소자로 입력된 기본 LO 주파수 $(f_{LO})$ 의 3차 고조파 성분 $(3f_{LO})$ 의 진폭이 최대가 되는 바이어스 전압을 선택하여 두 입력신호 $(f_{RF},\ f_{LO})$ 에 대해서 고차 출력신호성분 $(f_{RF}\pm 3f_{LO})$ 이 최대가 되는 고조파 믹서 $(harmonic\ mixer)$ 를 설계 및 제작하였다.

제안된 설계 방법에 의해서 제작된 고조파 믹서는 플라스틱(plastic) 패키지의 MESFET 소자를 사용하여 기존 Ka-대역에서 동작하는 믹서 회로들이 나타내는 높은 부품 가격, 생산성 및 회로의 복잡도 문제를 해결할 수 있었으며 RF 주파수신호( $f_{RF}$ =33.5GHz)에 대해서 LO 주파수 신호( $f_{LO}$ =11.5 GHz)의 3차 고조파 신호( $3f_{LO}$ =34.5 GHz)가 최대가 되는 게이트 바이어스 전압을 선택하여 중간주파수( $3f_{LO}$ - $f_{RF}$ =1.0GHz)에서 -10 dB의 낮은 변환 손실 특성을 나타내었다.

Key Words: harmonic mixer, Ka-band, multiplier, GaAs MESFET

#### **ABSTRACT**

In this paper, a Ka-band harmonic mixer is designed and fabricated on the base of the multiplier theory that there is a bias point to maximize the third harmonic order( $3f_{LO}$ ) with respect to a fundamental LO frequency( $f_{LO}$ ), which can make the high-order mixing element( $f_{RF} \pm 3f_{LO}$ ) to be greater than other mixing elements, pumping a RF frequency( $f_{RF}$ ) and LO frequency( $f_{LO}$ ).

The harmonic mixer by the proposed design method is fabricated by using a commercial GaAs MESFET device with a plastic package and overcome these disadvantages that a conventional mixer in Ka-band suffer from a high cost, inefficient productivity and circuit complexity. The harmonic mixer have a -10 dB conversion loss at the IF frequency( $3f_{LO}$ - $f_{RF}$ =1.0GHz) by selecting a gate bias voltage for the maximum third-order LO harmonic element( $3f_{LO}$ =34.5 GHz) as pumping LO frequency( $f_{LO}$ =11.5 GHz) with respect to RF frequency ( $f_{RF}$ =33.5GHz)

## I. 서론

최근 몇 년 사이에 마이크로웨이브 및 밀리미터 대역을 이용한 시스템 개발이 활발히 이루어지면서 초고주파 대역에서 동작하는 회로를 구현함에 있어 서 성능이외에도 가격 및 생산성에 대한 고려가 중 요한 설계 파라미터가 되고 있다<sup>11</sup>.

AP(Anti-Parallel) 다이오드를 이용한 SHP(Sub-Harmonically Pumped) 믹서는 낮은 LO 주파수, 낮은 스퓨리어스 특성을 갖기 때문에 초고주파 대역의 믹서회로에 많이 사용되고 있지만, 빔리드 형태의 AP(Anti-Parallel) 다이오드를 기판(Substrate)에

<sup>\*</sup> 인하대학교 전자공학과 초고주파 및 항공전자통신 연구실(sydney989@hanafos.com, int-ksy@hanmail.net, hdpark@inha.ac.kr) 논문번호: KICS2005-07-272, 접수일자: 2005년 7월 22일

본딩(bonding) 작업을 통하여 조립(Assembly)해야 하므로 추가적인 비용 및 생산성이 저하되는 단점 이 있다 $^{[2]}$ .

다른 방법으로 제안되고 있는 능동 소자를 이용한 SHP(Sub-Harmonically Pumped) 믹서는 반파장 (Half-wavelength) 전송선로 또는 발룬(balun)과 같은 위상천이회로를 사용하여 두개의 능동소자에 180 위상차를 갖는 LO 주파수를 인가시키는 구조이기 때문에 가격, 생산성 및 회로크기가 커지는 단점을 갖는다<sup>13</sup>.

본 논문에서는 주파수 채배기 이론에 근거하여 단일 능동소자로 입력된 기본 LO 주파수( $f_{LO}$ )의 3차 고조파 성분( $3f_{LO}$ )의 진폭이 최대가 되는 바이어스 전압을 선택하여 두 입력신호( $f_{RF}$ ,  $f_{LO}$ )에 대해서고차 출력신호성분( $f_{RF}$ ± $3f_{LO}$ )이 최대가 되는 고조파믹서(harmonic mixer)를 제안하였다. 제안된 고조파믹서는 두 입력신호( $f_{RF}$ ,  $f_{LO}$ )에 대해서 기본 출력신호성분( $f_{RF}$ ± $f_{LO}$ )의 진폭이 최대가 되는 기본믹서(fundamental mixer)에 비해서 낮은 LO 주파수를사용할 수 있으며, 단일 능동소자로 Plastic 패키지상용 GaAs MESFET 소자를 사용함으로서 비용 절감 및 생산성 향상을 꾀할 수 있다. 또한 추가적인위상천이 회로를 사용하지 않으므로 회로의 크기를줄일 수 있은 장점을 갖는다.

본 논문의 구성은 Ⅱ장에서는 제안된 고조파 믹서의 설계 방법에 대해서 설명하고 Ⅲ장에는 측정된 고조파 믹서의 성능에 대해서 언급하고 Ⅳ장에서 결론을 내린다.

### Ⅱ. 고조파 믹서 설계

## 2.1 고조파 믹서의 바이어스 전압

GaAs MESFET에서 고조파를 발생시키는 비선형 요소들 중에서 고조파 발생에 가장 많은 영향을 주는 요소는 전류원 IDS의 Clipping에 의한 비선형 특성이다. 게이트 바이어스 전압에 의한 드레인 전류성분에 포함되는 고조파 성분들은 출력전류 또는 출력전압 파형이 비대칭적으로 왜곡될 경우에는 짝수(even) 고조파 성분이 발생되고 대칭적으로 왜곡될 경우에는 짝수(even) 고조파 성분이 발생되고 대칭적으로 왜곡될 경우에는 홀수(odd) 고조파 성분이 발생되는데이러한 효과는 바이어스 전압에 의해서 제어된다[4].. 게이트전압(VGS)-드레인 전류(IDS) 전달 특성이선형적이고 고조파 발생이 드레인 전류의 클리핑(clipping)에 의해서만 발생한다고 가정했을 때 드레인 전류를 퓨리에 변환하면 식(1)과 같이 쓸 수 있

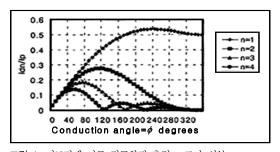

으며 $^{[5]}$ , 식 (1)로부터 피크 드레인 전류( $\Phi$ )로 정규화하여 전도각( $2\phi$ )에 따른 고조파 출력전류를 그림 1에 나타내었다.

$$\begin{split} I_n &= \frac{I\!p}{\pi} \; \{ \frac{\sin\left(\left[n-1\right]\pi t_0/T\right)}{n-1} + \frac{\sin\left(\left[n-1\right]\pi t_0/T\right)}{n+1} \\ &\qquad \qquad - \frac{2}{n} \left(\cos\left(\pi t_0/T\right) \sin\left(2\pi t_0/T\right)\right\} \end{split}$$

for  $n \neq 1$

$$I_{1} = \frac{I_{p}}{\pi} \left[ \frac{\pi t_{0}}{T} - \frac{\sin(2\pi t_{0}/T)}{2} \right]$$

(1)

그림 1에서 보듯이 각 고조파 출력 전류에 대한 전도각은  $2\Phi_{opt}=240^{\circ}/n$ 으로 근사적으로 구할 수 있기 때문에 3차 고조파 출력전류를 최대화시키기 위한 전도각은  $2\Phi=80^{\circ}$ 이다.

그림 1. 전도각에 따른 정규화된 출력 고조파 성분. Fig 1. Normalized harmonic current for conduction angle.

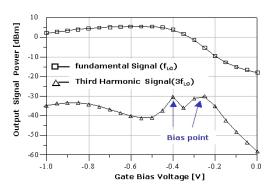

그림 2는 게이트 바이어스 전압을 가변시켰을 때기본 LO 신호와 3차 고조파(3f<sub>LO</sub>) 신호의 전력 레벨을 나타낸 것으로 특정 게이트 바이어스 전압에서 3차 고조파 성분이 최대가 되는 게이트 전압이존재함을 알 수 있다. 이 게이트 전압(V<sub>GS</sub>)을 고조파 믹서의 바이어스 전압으로 인가하였다.

그림 2. 게이트 바이어스 전압에 따른 고조파 신호레벨. Fig 2. Harmonic Level for gate bias voltage  $(V_{GS})$ .

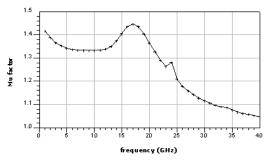

드레인단에서 발생되는 기본 국부발진 신호(file) 및 고조파 신호들의 궤환(feedback)에 의해서 회로가 불안정하게 되기 때문에 회로 입출력에 적절한 종단회로 및 이득 저하를 통한 안정화 회로를 적용하여 회로 안정도를 꾀하였다. 3차 고조파성분(3file)이 최대가 되는 게이트 바이어스 전압에서 발진 현상을 방지하기 위하여 고조파 성분들에 대해서 단락회로를 구성하였다. 그림 3은 모든 주파수 대역에서 안정도 계수가 1보다 크다는 것을 나태내고 있다.

그림 3. 고조파 믹서 안정도. Fig 3. The harmonic mixer stability.

# 2.2 3차 고조파 믹서의 구조

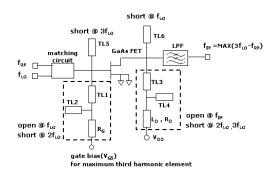

게이트 바이어스 전압은 체배기 이론을 이용하여 3차 고조파 신호가 최대가 되도록 설정하였으며 국부발진 신호(f<sub>Lo</sub>)와 RF 신호(f<sub>RF</sub>)가 게이트로 인가되고 중간주파수(f<sub>IF</sub>)는 드레인 단자에서 출력되도록하여 게이트 믹서 구조와 유사한 구조로 구현하였다.

그림 4는 제안된 고조파 믹서의 구성을 나타내었다. 국부발진신호( $f_{LO}$ )와 RF 신호( $f_{RF}$ )는 각각의 정합회로를 통과한 후 게이트 단자로 입력하였고 IF 신호( $3f_{LO}$ )는 드레인 단자에서 저역통과필터(LPF)를 거친 후 얻었다. 제안된 고조파 믹서 회로는 체배기 이론에 기초하여 3차 고조파 성분( $3f_{LO}$ )이 최대가 되는 게이트 바이어스 전압( $V_{CS}$ )을 선택하였다.

안정도 확인 후 각각의 RF, LO 및 IF 단자에 대한 정합회로를 설계하였다. LO 단자는 입력되는 신호 크기가 크기 때문에 대신호 산란계수를 이용하여 정합회로를 설계하였고 RF 및 IF 단자의 임피던스는 LO 신호 크기에 영향을 받기 때문에 준선형(quasi-linear) 설계 방법을 이용하여 정합회로를 설계하였다<sup>6</sup>.

상기에서 제안된 설계 방법으로 설계한 고조파 믹서는 국부발진신호(fLo)의 주파수는 11.5 GHz, RF 신호의 주파수는 33.5GHz에 대해서 RF 신호

그림 4. 제안된 고조파 믹서의 회로도. Fig 4. The proposed harmonic mixer configuration.

(11.5 GHz)와 국부발진 신호의 3차 고조파 성분  $(3f_{LO}=34.5 \text{ GHz})$ 과의 혼합(mixing) 성분이 최대가되도록 게이트 바이어스 전압을 선택하여 중간주파수( $f_{IF}=3f_{LO}-f_{RF}=1.0 \text{ GHz}$ )에서 최소의 변환손실 특성을 나타내도록 설계하였다.

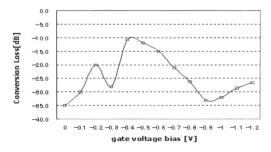

그림 5는 게이트 바이어스 전압의 변화에 따른 고조파 믹서의 변환손실 특성을 나타내었다. 그림 5(a)는 3차 고조파 성분(3f<sub>LO</sub>)에 의해서 발생되는

(b) 그림 5. (a) 고조파 믹서의 변환손실, (b) 기본파 믹서의 변 화소식

- (a) The conversion loss of harmonic mixer

- (b) The conversion loss of fundamental mixer

주파수 변환특성( $3f_{LO}\pm f_{RF}$ )을 나타낸 것으로 게이트 바이어스 전압( $V_{GS}$ )가 -0.5V에서 -10 dB정도의 변환손실 성능을 나타내고 있다. 그림 5(b)는 기본 고조파 혼합성분( $f_{LO}\pm f_{RF}$ )과 2차 고조파 혼합성분( $2f_{LO}\pm f_{RF}$ )의 변환손실 특성의 모의실험 결과를 나타내었다.

# Ⅲ. 측정결과

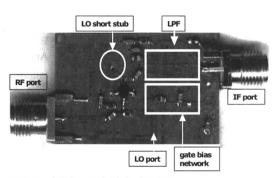

설계된 고조파 믹서 회로의 제작에 사용된 PCB 기판은 유전율 2.17, 기판 높이가 0.5 mm이고 도체 두께가 0.35 um인 테프론 기판을 사용하였다. 그림 6은 제작된 고조파 믹서의 실물도이다. 저역통과주 파수(LPF) 및 게이트 바이어스 회로들은 모멘텀(momentum) 해석을 하였으며 고조파 믹서 회로의 모 의실험은 Agilent사의 ADS(Advanced Design System)를 이용하였다.

그림 7은 LO 신호의 크기를 +5dBm으로 고정후 게이트 바이어스 전압의 변화에 따른 IF 출력주 파수(f<sub>RF</sub>±3f<sub>LO</sub>)에 최소의 변환손실 특성을 나타내었다. -0.4 V에서 -13 dBm 정도의 변환손실 특성을 나타내고 있지만 측정 케이블 손실을 고려한다면모의실험 결과와 유사한 -10 dBm 정도의 변환손실

그림 6. 제작된 고조파 믹서 실물사진 Fig 6. Photograph of fabricated harmonic mixer

그림 7. 게이트 바이어스 전압에 따른 변환손실 특성 Fig 7. the variation of the conversion gain with respect to gate bias voltage

특성을 나타내고 있으며 다른 게이트 바이어스 전 압에서의 변환손실 특성은 급격하게 감소하고 있음 을 알 수 있다.

게이트 바이어스 전압을 -0.4V로 고정시킨 후 LO 신호의 전력 변화에 따른 변환손실 특성을 그림 8에 나타내었고, 케이블 손실을 고려하지 않은 상태에서 LO 레벨이 +5 dBm~+10 dBm에서 -10 dB의 변환손실 특성을 나타내고 있다.

그림 8. LO 전력에 따른 변환손실 특성 Fig 8. the variation of the conversion gain with respect to LO power

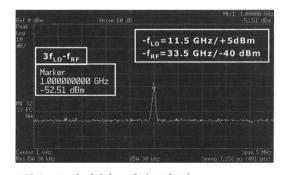

그림 9는 게이트 바이어스 전압은 -0.4 V, LO 신호 전력은 +5dBm, RF 신호 전력은 -40 dBm인 조건에서 케이블 손실을 고려하지 않고 측정한 IF 출력 스펙트럼을 나타내었다.

그림 9. 고조파 믹서의 IF 출력 스펙트럼 Fig 9. IF output spectrum of the harmonic mixer

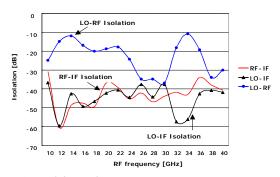

그림 10은 출력 스펙트럼을 측정하기 위해서 설정했던 측정 환경과 동일한 조건에서 측정한 각 단자간 격리도 특성을 나타내었다. 게이트 믹서의 단점인 RF-LO 분리도 특성이 RF-IF 분리도와 LO-IF 분리도에 비해서 특성이 나쁘다는 것을 알 수 있다.

표 1은 제안된 3차 고조파 믹서 회로의 설계값과 측정값을 비교 분석하여 요약하였다.

그림 10. 격리도 특성 Fig 10. Isolation performance

표 1. 제안된 고조파 믹서 특성요약

Table 1. Summary of the proposed harmonic mixer

| 항목                         |       | 설계값      | 측정값    |  |  |  |  |  |

|----------------------------|-------|----------|--------|--|--|--|--|--|

|                            | RF    | 33.5 GHz |        |  |  |  |  |  |

| 주파수                        | LO    | 11.5 GHz |        |  |  |  |  |  |

|                            | IF    | 1.0 GHz  |        |  |  |  |  |  |

| LO 전력                      |       | 0 dBm    | 5 dBm  |  |  |  |  |  |

| 이득                         |       | -10dB    | -10dB  |  |  |  |  |  |

| 1dB 압축점(P <sub>1dB</sub> ) |       | 5 dBm    | 0 dBm  |  |  |  |  |  |

| 분리도                        | LO-RF | -        | -10dBm |  |  |  |  |  |

|                            | LO-IF | -        | -58dBm |  |  |  |  |  |

|                            | RF-IF | -        | -43dBm |  |  |  |  |  |

# Ⅳ. 결 론

본 논문에서는 기존 고조파 믹서 설계 방법과는 다른 체배기 이론에 의한 바이어스 설정을 통한 설계 방법을 적용하였다. 제안된 고조파 믹서는 기본 국부발진 주파수( $f_{LO}$ =11.5 GHz)의 3차 고조파 성분 ( $3f_{LO}$ =34.5 GHz)이 최대가 되는 게이트 바이어스 전압을 선택하여 Ka 대역( $f_{RF}$ =33.5 GHz)신호를 중간 주파수( $f_{IF}$ =3 $f_{LO}$ - $f_{RF}$ =1GHz)에서 -10 dBm의 변환 손실 특성을 갖는 3차 고조파 믹서를 설계 및 제작하였다. 표 2는 다른 논문에서 제안된 고차 고조파

믹서들의 성능변화를 비교 분석하여 나타내었다. 기존 발표된 고조파 믹서들은 PHEMT 파운드리 (Foundary)를 사용하여 MMIC(Monolithic Microwave Integrated Circuit)기법으로 설계하거나 APD (Anti-Parallel Diode)나 쇼키트 다이오드(Schottky Diode)같은 칩(chip) 형태의 소자를 본딩(bonding)과 같은 작업을 통하여 하이브리드(Hybride) 방법으로 제작하기 때문에 가격 및 생산성 측면에서 문제점을 갖고 있다.

제안된 고조파 믹서는 체배기 이론을 기반으로 최적의 바이어스 지점을 선택하여 변환손실 특성 뿐 만아니라 플라스틱 재질의 패키지 소자인 상용 GaAs MESFET 소자를 사용하여 가격, 생산성 및 복잡도 측면에서 다른 발표 논문들에 비해 많은 장 점들을 가지고 있어 양산제품에 적용할 수 있으리 라 판단된다.

#### 참 고 문 헌

- [1] A R Barnes, P Munday, R Jennings and M T Moore, "A comparison of W-band monolithic resistive mixer architectures", IEEE MTT-S Digest, pp.1867-1870, 2002.

- [2] Ji-Young Park, Seong-Sik Jeon, Yuanxum Wang, and Tatsuo Itoh, "Millimeter Wave Direct Quadrature Integrated with Antenna for Broad-Band Wireless Communications," IEEE MTT-S Digest, pp.1277-1280, 2002.

- [3] K.S Ang, A.H. Baree, S. Nam and I.D. Robertson, "A Millimeter-Wave Monolithic Sub-Harmonically Pumped Resistive Mixer," in 1999 Int. Microwave Symp.Dig., pp. 222-225.

- [4] Anand Gopinath, "Single-gate MESFET FET frequency doublers," IEEE Trans. Microwave Theory Tech. Vol. MTT-30, no. 6, pp.

표 2. 고차 고조파 믹서 논문들의 성능비교 Table 2. Performance comparison with other papers

| 특성<br>비교  | 대역 (GHz) | 소자                  | 차수 | 이득 (dB) | 구현기술      | LO(dBm) |

|-----------|----------|---------------------|----|---------|-----------|---------|

| [7]       | 38~38.16 | PHEMT               | 2  | -15     | MMIC      | 4       |

| [8]       | 41.5     | APD chip            | 3  | -16     | Hybrid    | 6       |

| [9]       | 36-40    | APD chip            | 2  | -9.5    | MMIC      | 6       |

| This Work | 33-34    | MESFET with package | 3  | -10     | Soldering | 5       |

8692-874, June 1982.

- [5] E. O'Ciardha, "Generic-device frequency multiplier analysis-a unified approach," IEEE Trans. Microwave Theory Tech., Vol. MTT-48, no. 7, pp.1134-1141, July 2000.

- [6] Yew Hui Liew and Jurianto Joe, "RF and IF Ports Matching Circuit Synthesis for a Simultaneous Conjugate-Matched Mixer Using Quasi-Linear Analysis," IEEE Trans. Microwave Theory and Tech., Vol. 50, no.7, pp.2056-2062, September 2002.

- [7] Yon-Lin Kok, Morteza Ahma°, Huei Wang, Barry R. Allen, Tzuen Lin, "A Ka-Band Monolithic Single-Chip Transceiver Using Sub-harmonic Mixer," IEEE MTT-S Digest, pp.309-311, 1998.

- [8] Pascual M.L, Hartnagel H.L, "An Optimal Mixer Matching Design Technique Under Large Signla Pumping," rfdesign Journal, pp.28-38, Jan 2003.

- [9] Kenji Itoh, Akio Iida, Yoshinobu Sasaki, Shuji Urasaki, "A 40GHz Band Monolithic Even Harmonic Mixer with An Antiparallel Diode Pair," IEEE MTT-S Digest, pp.879-882, 1991.

#### 고 민호(Min-Ho Go)

정회원

1995년 2월 여수대학교 전자통 신공학과(공학사)

1997년 2월 인하대학교 전자공 학과(공학석사)

2003년~현재 인하대학교 전자 공학과(박사과정)

<관심분야> 무선통신 시스템 설

계, 초고추파 회로설계, RFIC 설계, 안테나 설계

## 강 석 엽(Suk-Youb Kang)

정회원

1997년 2월 인천대학교 전자공 학과(공학사)

1999년 2월 인하대학교 전자공 학과(공학석사)

2005년 8월 인하대학교 전자공 학과(공학박사)

<관심분야> 무선통신 시스템 설

계, RF 및 초고추파 회로설계, 안테나 설계, RFIC 설계

#### 박 효 달(Hyo-Dal Park)

정회워

1978년 2월 인하대학교 전자공 학과(공학사)

1987년 (불) 국립항공우주대학 전자공학과(공학박사)

1992년~현재 인하대학교 전자 공학과 교수

<관심분야> 항공통신 시스템 설

계, 초고주파 회로 설계, 전자장 이론, 안테나공학