## Triple Error Correcting Reed Solomon Decoder Design Using Galois Subfield Inverse Calculator And Table ROM

Hyeong-Keon An\* Reguler Member, Young-Jin Hong\*\* Lifelong Member

### ABSTRACT

A new RS(Reed Solomon) Decoder design method, using Galois Subfield GF(24) Multiplier, is described. The Decoder is designed using Normalized error position stored ROM. Here New Inverse Calculator in  $GF(2^8)$  is designed, which is simpler and faster than the classical  $GF(2^8)$  direct inverse calculator, using the Galois Subfield GF(2<sup>4</sup>) Arithmatic operator.

Key Words: RS(Reed Solomon), Syndrome, Encoder, Decoder, Inversion, Error Locator polynomial, Galois Field(GF)

### I. Introduction

Reed Solomon coding theory is very famous well known nonbinary error correction method for Digital Electronic Devices(Consumer and Communication products.)<sup>[3]</sup>.

In this paper, new RS(Reed Solomon) Decoder, which is correcting 3 symbol errors, design method is proposed using Normalized error position stored ROM<sup>[2]</sup>. Especially new Inverse calculator in GF  $(2^8)$  is implemented using its Galois Subfield GF(2<sup>4</sup>) Arithmatic operator. The new Subfield operator is much simpler and faster than before, So More efficient RS Decoder design is Possible<sup>[1]</sup>.

In chapter 2, we briefly described RS(Reed Solomon) ECC algorithm. For example we describe how to calculate syndromes, solve Newtonian identitiy equations.

In chapter 3,we describe the New RS Decoder algorithm which is correcting 3 symbol error in the codeword. Example is showing the algorithm is working well. In MD(Mini Disc Player), DCC,

HDTV, Main computer magnetic storage system, this 3 symbol error correcting RS decoder is used.

In chapter 4, the new Inverse calculator, in  $GF(2^8)$ , design method is described. Dividing can be done using Multiplier and this inversion circuit. Definitely the new circuit, using Galois subfield GF(2<sup>4</sup>) arithmetic operator, is much more efficient than the direct  $GF(2^8)$  operator. For more clarity, we show inversion example to describe the step of the algorithm.

In chapter 5 conclusions are made. Future works on 4 symbol error correcting RS decoder is briefly mentioned. Also Divider in GF(2<sup>8</sup>) design method is also discussed.

II. Syndromes and Error Locator polynomial

An RS(Reed Solomon) codes are based on finite fields, often called Galois fields.

In CDP, RSC(32,28), on  $GF(2^8)$  field, codes is used and up to 2 symbol errors can be corrected [2]

Copyright (C) 2006 NuriMedia Co., Ltd.

<sup>\*</sup> Department of Information & Communications Engineering, College of Engineering (hkan@tit.ac.kr)

<sup>\*\*</sup> Department of Information Security, College of Engineering (gryjhong@tit.ac.kr) 논문번호 : KICS2005-10-423, 접수일자 : 2005년 10월 19일

An RS code with 8bit symbols will use a Galois field  $GF(2^8)$ , consisting of 256 symbols. In decoding Reed-Solomon code, we should calculate the Syndromes as in equation 1.

Let

$$C(X) = \sum_{j=0}^{n-1} C_j X^j$$

Be the Transmitted polynomial, and let

$$r(X) = \sum_{j=0}^{n-1} r_j X^j$$

Be the received polynomial. Then error pattern of the channel is

$$E(X) = \sum_{j=0}^{n-1} E_j X^j$$

Where  $E_j(j=0 \text{ to } n-1)$  are error values. Here Syndromes are defined as

$$S_i = E(\alpha^i) (i=0,1,\dots, 2t-1) \dots$$

(1)

For t error correction coding.

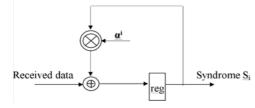

In this paper, for finding Error values and positions, syndrome calculator shown in Fig. 1 is used<sup>[3, 6]</sup>.

Fig. 1. Syndrome calculator of RS codec

Now if there are t errors, error values are  $E_n$  (n=0, 2…, t-1) and their positions are  $\alpha^{jn}$ (n=0,1, …, t-1).

Then Let

$$\beta_j(j=0,1,\dots, t-1) = \alpha^{jn}(n=0,1,\dots,t-1)$$

and Error Locator polynomial is defined as

$$\delta(\mathbf{X}) = (\mathbf{X} - \beta_0)(\mathbf{X} - \beta_1) \cdots (\mathbf{X} - \beta_{t-1}) = \sum_{k=0}^{t} \mathbf{X}^k \delta_{t-k} \cdots$$

(2)

Now Newton's identities are following set of equations.

$$\sum_{j=1}^{t} S_{t-j+v} \delta_{j} = S_{v+t} (v=0, 1, 2..., t-1)...$$

(3)

These equations are for t error correcting Reed-Solomon codec<sup>[4, 5]</sup>. If we apply these equations to 3 symbol error correction case (t=3), all the  $\delta_i$ (i=1, 2, 3) are got as described in the next section<sup>[7]</sup>.

### III. Triple Error Correcting Reed Solomon Decoder Design

In  $GF(2^8)$ , If there are 3 symbol errors in the received codeword, we can find 3 error positions and

Error values as follows<sup>[7]</sup>.

Here we use ROM tables as in 2 symbol error case<sup>[2]</sup>.

In this case, Error Locator polynomial is

$$X^{3} + \delta_{1}X^{2} + \delta_{2}X + \delta_{3}=0 \cdots$$

(4)

Here

$$\begin{split} \delta_1 &= (S_1S_3^2 + S_1^2S_5 + S_2^2S_3 + S_0S_2S_5 + \\ S_0S_3S_4 + S_1S_2S_4) \ / \ \chi, \\ \delta_2 &= (S_0 S_4^2 + S_2S_3^2 + S_2^2S_4 + S_0S_3S_5 + \\ S_1S_2S_5 + S_1S_3S_4) \ / \ \ \chi, \end{split}$$

$$\delta_3 = (S_3^3 + S_1 S_4^2 + S_2^2 S_5 + S_1 S_3 S_4) / \chi \cdots (4-1)$$

where  $\chi = S_2^3 + S_0 S_3^2 + S_1^2 S_4 + S_0 S_2 S_4$ .

From equation 13, if  $X=\delta_1+y$ , also if (E =  $\delta_1^2 + \delta_2$ ,  $\delta=\delta_1 \delta_2 + \delta_3$  then We get

$$Y^3 + (EY + \delta = 0 \cdots$$

(5)

If  $(E=0, Y=(\delta)^{1/3})$ , otherwise Let's define  $Z_i = (E^{-1/2}, Y_i)(i=1,2,3)$

$$Z^{3} + Z + \delta / E^{3/2} = 0 \cdots$$

(6)

From Equation 6, corresponding to Add=  $\delta/\mathbb{C}^{3/2}$ we can construct ROM table of root of equation (6) as in Fig. 2.

### Copyright (C) 2006 NuriMedia Co., Ltd.

www.dbpia.co.kr

#### <Zi ROM table>

| Address( $\delta / \times^{3/2}$ ) | data (Z <sub>i</sub> , i=1,2,3)                        |

|------------------------------------|--------------------------------------------------------|

| 0                                  | 0,1,1                                                  |

| 1                                  | •                                                      |

| a                                  | •                                                      |

| a <sup>2</sup>                     | •                                                      |

| •                                  | •                                                      |

| •                                  | •                                                      |

| •                                  | •                                                      |

| a <sup>239</sup>                   | a <sup>157</sup> , a <sup>181</sup> , a <sup>156</sup> |

| •                                  | •                                                      |

| a <sup>254</sup>                   | •                                                      |

Fig. 2. ROM table corresponding to equation 6. When Address = 0, Only 2 roots exist.

Once we find  $Z_i(i=1,2,3)$ ,  $Y_i(i=1,2,3)= \times^{1/2} Z_i$ So exact Error positions are

$$X_i = Y_i + \delta_1 \quad (i = 1, 2, 3) \quad \cdots \qquad (7)$$

Also Error values are

$$E_{i} = (S_{0}\delta_{3}/X_{i} + S_{1}(\delta_{1} + X_{i}) + S_{2})/(X_{i}^{2} + \delta_{2}) \quad (i=1,2,3) \quad \cdots \quad (8)$$

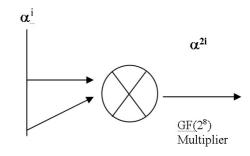

As we see, there are many GF(2<sup>8</sup>) Arithmatic operations to compute the Error values and positions. In Fig. 3. we show how to compute square values. Other operations needed are  $\alpha^{1/2}$ ,  $\alpha^{i}/\alpha^{i}$ . Allthese operations can be done using only Inverse calculator and Multiplier.

Next section, we show how to compute inversion values and  $GF(2^8)$  division.

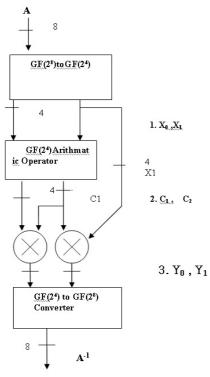

In Fig. 4  $GF(2^8)$  Inversion circuit diagram is shown using subfield  $GF(2^4)$  arithmetic operator, so those circuit can be implemented very efficiently <sup>[1]</sup>.

<Square ROM table>

| Address a <sup>i</sup> | Data a <sup>2i</sup> |

|------------------------|----------------------|

| 0                      | 0                    |

| 1                      | 1                    |

| a                      | a²                   |

| a <sup>2</sup>         | a <sup>4</sup>       |

| a <sup>3</sup>         | a <sup>6</sup>       |

| •                      | •                    |

| •                      | •                    |

| a <sup>254</sup>       | a <sup>253</sup>     |

Fig. 3. Square calculator with and without ROM

1) Square calculation using ROM

2) Square calculation with Multiplier

<Example> Triple Error correcting Reed Solomon Decoder example :

From the Transmitter, we send all 0 data so Code polynomial C(x)=0. In Receiver, Received polynomial  $R(x)=\alpha + \alpha x + \alpha^2 x^2$ .

In this case, find 3 error values and positions. All code symbols are 8 bits wise so  $GF(2^8)$  field elements are used.

<Solution>

We first find Syndromes :  $S_0 = \alpha^2$ ,  $S_1 = \alpha + \alpha^2 + \alpha^4 = \alpha^{239}$ .  $S_2 = \alpha^{37}$ ,  $S_3 = \alpha^{75}$ ,  $S_4 = \alpha^{219}$ ,  $S_5 = \alpha^{24}$ . From Equations (4-1 ), we find out  $\delta_1 = \alpha^{198}$ ,  $\delta_2 = \alpha^{199}$ ,  $\delta_3 = \alpha^3$ . So from equations (5),  $(E = \alpha^{248}, \ \delta = \alpha^{101})$ . Hence  $\delta/(E^{3/2} = \alpha^{239})$ .

So from following equation,

$$Z^3 + Z + a^{239} = 0.$$

So Using ROM table in fig. 5, we find that  $Z_i = \alpha^{157}$ ,  $\alpha^{181}$ ,  $\alpha^{156}$ .

Therefore

$$Y_i = \mathbb{E}^{1/2} Z_i = \alpha^{26}, \alpha^{50}, \alpha^{25} (i=1,2,3).$$

So from equation (7),

$$X_i=Y_i+\delta_1$$

(i=1,2,3) =  $a^0$ ,  $a^1$ ,  $a^2$ .

These are 3 correct Error positions and 3 error values are calculated from equation (8), as  $\alpha$ ,  $\alpha$ ,  $\alpha^2$ . These are also correct 3 error values as we see from received polynomial r(x).

### Copyright (C) 2006 NuriMedia Co., Ltd. www.dbpia.co.kr

# **IV**. New GF(2<sup>8</sup>) Inverse element calculating circuit design

In this section, we describe how to simplify the Inversion circuit using Galois subfield<sup>[1]</sup>. The circuit is used for divider HW in RS Codec. Using this and multiplier described in the former Author's paper<sup>[2]</sup>, Most RS Codec circuit can be simplified and faster. In Fig. 5 we draw the New inversion circuit block diagram<sup>[1]</sup>. Here all arithmetic operationa are done in  $GF(2^4)$  field so Dramatically reducing gate counts and computational speed much faster than the case in  $GF(2^8)$ . Multipler design using  $GF(2^4)$  Sub field is described in the Author's another paper<sup>[2]</sup>.

Fig. 4. Inversion Circuit in  $GF(2^8)$ 1. X0,X1 each 4 bits 2. C1=((X0+X1)X0+  $_XX1^2)^{-1}$ ,C2=X0+X1

$GF(2^8)$  to  $GF(2^4)$  is processed as follows.

Let  $\alpha^k$  is in GF(2<sup>8</sup>) field as (b<sub>0</sub>, b<sub>1</sub>, ..., b<sub>7</sub>), it can be expressed as  $\alpha^k = a + b\beta$  where a and b is in GF(2<sup>4</sup>) field and  $\beta$  is in GF(2<sup>8</sup>). Here a and b are (z<sub>0</sub>,z<sub>1</sub>,z<sub>2</sub>,z<sub>3</sub>) and (z<sub>4</sub>,z<sub>5</sub>,z<sub>6</sub>,z<sub>7</sub>) respectively. All b<sub>j</sub>, Then

$$Z_{0} = b_{0}+b_{1}+b_{5}$$

$$Z_{1} = b_{1}+b_{3}+b_{5}$$

$$Z_{2} = b_{2}+b_{3}+b_{6}$$

$$Z_{3} = b_{1}+b_{3}+b_{4}+b_{6}$$

$$Z_{4} = b_{1}+b_{2}+b_{3}+b_{5}+b_{6}+b_{7}$$

$$Z_{5} = b_{2}+b_{5}+b_{6}$$

$$Z_{6} = b_{1}+b_{2}+b_{3}+b_{4}+b_{5}+b_{6}$$

$$Z_{7} = b_{1}+b_{3}+b_{4}+b_{5} \dots$$

(9)

In the same way, From (9), we find  $GF(2^4)$  to  $GF(2^8)$  converter equation is, for example

$$B_{0} = Z_{1} + Z_{0} + Z_{2} + Z_{6} + Z_{7}$$

$$B_{1} = Z_{2} + Z_{1} + Z_{5}$$

$$B_{2} = Z_{3} + Z_{5} + Z_{7}$$

$$B_{3} = Z_{2} + Z_{6} + Z_{7}$$

$$B_{4} = Z_{1} + Z_{7}$$

$$B_{5} = Z_{5} + Z_{6} + Z_{7}$$

$$B_{6} = Z_{3} + Z_{6} + Z_{5}$$

$$B_{7} = Z_{1} + Z_{6} + Z_{4} + Z_{7} \dots$$

(10)

Now A,  $A^{-1}$  in  $GF(2^8)$  can be expressed as follows.

$$A = X_0 + X_{1\beta} A^{-1} = Y_0 + Y_{1\beta} ...$$

(11)

So

$$X_0 Y_0 + {}_{\mathcal{X}} X_1 Y_1 = 1$$

$$X_1 Y_0 + (X_0 + X_1) Y_1 = 0 \cdots$$

(12)

Here X<sub>0</sub>, X<sub>1</sub>, Y<sub>0</sub>, Y<sub>1</sub>  $\in$  GF(2<sup>4</sup>),  $\beta$ and  $\chi \in$  GF (2<sup>8</sup>) also  $\beta^2 = \beta + \chi$ , then Y<sub>0</sub>, Y<sub>1</sub> are represented as in (13)<sup>[1]</sup>:

$$Y_{0}=(X_{0}+X_{1})/B$$

$$Y_{1}=X_{1}/B$$

(13)

$$B=X_{0}(X_{0}+X_{1})+\chi(X_{1}^{2}) ...$$

Also if X=(  $x_0$ ,  $x_1$ , $x_2$ , $x_3$ ),  $\forall X^2$ =(  $x_2+x_3$ ,  $x_0 + x_2 + x_3$ ,  $X_3$ ,  $x_1 + x_2$ ).

### Copyright (C) 2006 NuriMedia Co., Ltd.

www.dbpia.co.kr

11

All these are implemented in Fig. 4.

Fig. 5 is a Divider circuit using this inversion circuit.

Fig. 5. Divider Circuit in  $GF(2^8)$  using Circuit in Fig. 4, where  $A,B \in GF(2^8).$

if we compare the Number of gates when we compute  $Y=A^2B \in GF(2^8)$  between two cases GF (2<sup>4</sup>) transformation case and  $GF(2^8)$  case (Two Multipliers are used),

### 1) $GF(2^8)$ case

The total number of gates breaks down as follows.

| AND gate  | EXOR gate |

|-----------|-----------|

| 2X64 =128 | 2X73=146  |

2)  $GF(2^4)$  transformation case

| AND                                                  | EXOR |

|------------------------------------------------------|------|

| $GF(2^8)$ to $GF(2^4)$                               | 13   |

| 2Multiplier(GF(2 <sup>4</sup> )) 48X2                | 65X2 |

| $\operatorname{GF}(2^4)$ to $\operatorname{GF}(2^8)$ | 13   |

| 96                                                   | 156  |

So totally 22 gates are saved when we use  $GF(2^4)$  transformation method. This cost reduction is even further larger if the computation becomes more complex<sup>[1]</sup>.

#### <Example>

Let's Find Inverse of  $\alpha^5$ ,  $\alpha^{-5} \in GF(2^8)$  using Subfield  $GF(2^4)$  Arithmatic operation.

<Solution>

A =  $a^5 \in GF(2^8) = X_0 + X_1 \beta$ .

From Eq 9.,  $X_0 = a^{12}$ ,  $X_1 = a^6 \in GF(2^4)$ .

From Eq 13.,  $Y_0 = a^{14}/(a^{13} + a^{12} a^{14}) = a^9$ ,

Here  $\chi X_1^2 = a^{13}$ .

Also  $Y_1 = 1/(a^5 + a^7) = a^{-14} = a$ .

Now Convert these to element in  $GF(2^8)$ .

Then  $b_0 = b_1 = b_4 = b_7 = 0$  and  $b_2 = b_3 = b_5 = b_6 = 0$ .

Hence this  $b_i$  (i=0 to 7) represents  $\alpha^{250}$  =  $\alpha^{-5}$  so Correct.

### V. Conclusions

With the implementation of the inverse Calculator<sup>[1]</sup>, the divider can be easily implemented with multiplier circuit by using the subfield  $GF(2^4)$  arithmetic operation.

The idea presented in the paper simplifies the circuit and performs high speed operation by decreasing the number of logic gates<sup>[1]</sup>. The drawback of this transformation method is there is no advantage when the arithmatic computation is simple because in this, we should transpose  $GF(2^8)$  to  $GF(2^4)$  and inverse transpose  $GF(2^4)$  to  $GF(2^8)$  too.

Also RS 3 Symbol Error correcting Decoder can be implemented by using the circuit of table ROM. And this kind of 3 symbol Error correction RS decoder is used for most of the Current Digital Audio/Video devices, CDP, MP3, MD, HDTV, etc.

Our future works will be 4 symbol error correcting RS decoder, and direct  $GF(2^8)$  Divider using also  $GF(2^4)$  sub field, resulting in even further greately reducing RS codec HW circuitry<sup>[3]</sup>.

### REFERENCES

- US patent number 5227992, "Operational Method and Apparatus over GF(2<sup>m</sup>) using a Subfield GF(2<sup>m/2</sup>)", Man-young Lee, Hyeong-Keon An et al., 1993 Jul. 13

- [2] Hyeong-Keon An, "2 Error Correcting RS Decoder design", IDEC Conference Paper, KOEX, October 20-24, 2004

- [3] Hyeong-Keon An, TS Joo et al, "The New RS Ecc Codec For Digital Audio and Video", IEEE CES Conference paper, PP. 112-115, 1992

- [4] Lee Man Young, "BCH coding and Reed-Solomon Coding theory," 1990, Minumsa (Daewoo Academic Press).

- [5] Sunghoon Kwon and Hyunchul Shin, "Anarea-efficient VLSI architecture of Reed-Solomon decoder/encoder for digital VCRs," IEEE Transactions on Consumer Electronics, Vol. 43, No.4, Nov. 1997

- [6] Kwang Y.Liu, "Architecture for VLSI design of Reed-Solomon Decoders, "IEEE Transactions on Computers. Vol.33, No.2, Feb. 1984

- [7] 岡野博: ROM used 2 to 3 error correcting BCH Decoder Improvement, 信學技報, AL 82-56 (1982).

- [8] Shu Lin, Daniel J. Costello, Jr., "Error Control Coding," Prentice-Hall, pp.240-261 (20044).

#### An Hyeong-Keon

Reguler Member

He received B.Engineering Degree in electrical engineering from Seoul National University, Seoul, KOREA, in 1979 and M.S degree in electrical science from Korea Advanced Institute of Science and Technology, Seoul,

Korea in 1981, and the Ph.D. degree in electrical engineering from State University of New York at Stony Brook, NY, USA., in 1988. In 1988, he joined Samsung Electronics Co.Ltd as a Senior Researcher working for designing System LSI for 10 years. From 1998 to 1999, He worked for Telson Electronics Corp. working for CDMA handphone design. In 2000, he joined Tong Myoung University in Busan as a Professor in Dept. Of Information and Telecommunication engineering He has interests in designing CDMA and GSM hand phone and also in System LSI(Non Memory) design. He also operates Venture Comapany for Producing various Mobile phones and GPS/MP3 Engines.

Hong, Young-Jin

### Lifelong Member

He received the B. S. E. E. degree from Seoul National University. Seoul. Korea, in 1978 and the M. S. E. E. and Ph. D.(E. E.), from the State University of New York at Stony Brook in 1982 and 1985, respectively.

From January 1986 until May 1986 he was with the Department of Electrical Engineering at the State University of New York ay Stony Brook, as an Assistant Professor. In June 1986 he joined LNR Communications, Inc., Hauppauge, NY, where he was a Research Staff Engineer and working on spread spectrum systems and satellite communications. In 1992 he came back to Korea to join Samsung Advanced Institute of Technology (SAIT), where he had been leading several research projects including CT2, VSAT and TDMA cellular basestations for two years. Since then he has broadened the spectrum of his career path to include not only the area of R&D(CTO of Eastel Systems from 1994 through 1997; CTO of Sungil Telecom in the year of 2004) sector but also the business area(executive managing director of SKC&C from 1997 to 2003). He is currently an Associate Professor in the Department of Electrical and Electronics Engineering, Tongmyong University, Busan, Korea. His research interests are in the areas of smart antenna system, adaptive signal processing and communication systems. Dr. Hong is a member of Korean Institute of Communication Sciences, The institute of Electronics Engineers of Korea. he is also a member of IEEE.