# DLL 기반의 듀티 보정 회로를 적용한 무선랜용 I/Q 채널 12비트 40MS/s 파이프라인 A/D변환기

정회원 이 재 용\*, 준회원 조 성 일\*\*, 박 현 묵\*\*, 정회원 이 상 민\*\*, 윤 광 섭\*\*

## An I/Q Channel 12bit 40MS/s Pipeline A/D Converter with DLL Based Duty-Correction Circuit for WLAN

Jae-yong Lee\* Regular Member, Sung-il Cho\*\*, Hyun-mook Park\*\* Associate Members, Sang-min Lee\*\*, Kwang-sub Yoon\*\* Regular Members

요 약

본 논문에서는 무선 통신 분야의 WLAN/WMAN 시스템에 집적화할 수 있도록 I/Q 채널 12비트 40MS/s 파이 프라인 아날로그-디지털 변환기를 제안하였다. 제안하는 A/D 변환기는 높아진 동작 속도와 CMOS 소자의 최소 선폭이 작아지며 생기는 듀티 사이클의 변화를 보정해 줄 수 있는 DLL 기반의 듀티 사이클 보정 회로를 집적화하였다. 입력 듀티 사이클이 1%에서 99%까지 변동이 있어도 정확한 50%의 듀티 사이클을 가진 신호로 보정 가능하도록 설계하였다. 제작된 A/D 변환기는 0.18/m CMOS n-well 1-poly 6-metal 공정으로 제작되었으며, 전력소모는 1.8V 전원 전압에서 184mW이다. 샘플링 및 입력 주파수가 각각 20MHz, 1MHz 일 때 52dB의 SNDR과 59dBc의 SFDR을 나타내었다.

Key Words: ADC(Analog-to-Digital converter), Pipeline, DLL(Delay locked loop), CMOS, Duty-correction

#### **ABSTRACT**

In this paper, an I/Q channel 12bits 40MS/s Pipeline Analog to Digital Converter that is able to apply to WLAN/WMAN system is proposed. The proposed ADC integrates DLL based duty-correction circuit which corrects the fluctuations in the duksty cycle caused by miniaturization of CMOS devices and faster operating speeds. It is designed as a 1% to 99% input clock duty cycle could be corrected to 50% output duty cycle. The prototype ADC is implemented in a 0.18µm CMOS n-well 1-poly 6-metal process and dissipates 184mW at 1.8V single supply. The SNDR of the proposed 12bit ADC is 52dB and SFDR of 59dBc (@Fs=20MHz, Fin=1MHz) is measured.

### I. 서 론

최근 급속히 성장하고 있는 무선 트랜시버 시스 템은 아날로그와 디지털 기능의 더 높은 집적화 수 준을 요구하고, 멀티미디어라는 높은 서비스 품질을 위해 전송 속도와 전송 품질 역시 고성능을 목표로 나아가고 있는 실정이다. 멀티미디어 서비스를 좋은 품질로 제공하기 위해서는 고속의 데이터 통신이 요구되기에 무선 트랜시버 시스템의 광대역화가 필 수적인 것이다. 무선 트랜시버 시스템의 광대역화가

논문번호: KICS2007-12-546, 접수일자: 2007년 12월 6일, 최종논문접수일자: 2008년 4월 25일

<sup>※</sup>본 연구는 지식경제부 및 정보통신연구진흥원의 대학 IT연구센터 지원 사업의 연구결과로 수행되었음. (IITA-2008-C1090-0801-0019) \* 페어차일드 코리아 반도체, \*\* 인하대학교 전자공학과 정보전자 공동 연구소

이루어지기 위해서는 전단부의 신호처리를 맡고 있는 데이터 변환기의 광대역화가 선행되어야 하는 것이다. 무선통신용 트랜시버에 사용되는 데이터 변환기는 고속, 고해상도를 가지는 고성능 A/D 변환기가 요구된다<sup>1-21</sup>. 기존의 다양한 A/D 변환기 구조중에서 12비트의 해상도 및 40MS/s 수준의 동작속도 조건을 동시에 만족하기 위해서는 파이프라인구조가 많이 사용되고 있는 추세이다.

특히 높은 샘플링 주파수로 동작하는 스위치드 커패시터(switched capacitor) 기반의 파이프라인 구 조의 A/D 변환기는 스테이지간 하나의 클럭과 그 반대 위상의 클럭을 쓰기 때문에 칩 내에서 클럭의 정확한 50%의 듀티 사이클을 유지하는 것이 점점 중요해지고 있다.

기존의 듀티 보정 회로<sup>13</sup>는 상대적으로 좁은 보정 범위 (30-70%) 와 노이즈와 공정, 전원 전압, 온도 (Process, Voltage, Temperature : PVT) 변동에 민감하다. 본 연구에서는 듀티 사이클 보정 회로 앞단에 T-FF(Toggle Flip-flop) 을 사용하여 듀티 사이클 보정 범위를 1-99%까지 크게 하였다. 또한 완전 차동 구조의 전압 제어 지연 회로, 하프-레플리카 구조의 바이어스 단, 온칩 기준 전류 발생기(Bandgap reference)를 사용하여 노이즈와 PVT 변동에 영향이 최소화 되도록 설계하였다.

제안하는 A/D 변환기의 구조와 듀티 보정 회로의 자세한 설명은 Ⅱ장에 소개하였다. Ⅲ장은 플로 플랜과 레이아웃 방법에 대하여 논의하였고, Ⅳ장은 설계된 12비트 A/D 변환기의 측정 결과를 기술하였다. 그리고 마지막 Ⅴ장에서는 결론을 맺었다.

## Ⅱ. 제안하는 12비트 A/D 변환기의 설계

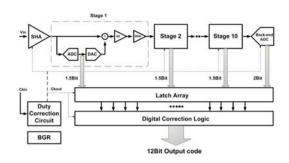

본 논문에서 제작된 12비트 40MS/s 파이프라인 ADC는 그림 1에서 나타낸 것처럼 듀티 사이클 보정 회로, 온칩 기준 전류 발생기<sup>(4)</sup>, 입력단의 샘플/홀드 증폭기 (Sample-and-hold amplifier : SHA), 1.5비트 구조를 가지는 10개의 스테이지, 디지털 신호의 동시 출력을 위한 래치회로 및 오차보정회로 (Digital error Correction Circuit : DCL)로 구성되어 있다<sup>(5-7)</sup>.

파이프라인 A/D 변한기의 각 스테이지는 1.5비 트 또는 멀티비트로 구현될 수 있다. 본 논문에서는 각 스테이지를 1.5비트로 구성할 것이며, 1.5비트의 장점으로는 설계 방법의 가장 간결한 구조로써 소자의 수, 비교기의 저항 수를 줄일 수 있으며, 연산

그림 1. 12비트 파이프라인 A/D 변환기의 블록 다이어그램 Fig. 1. Block diagram of the 12bit pipelined A/D converter

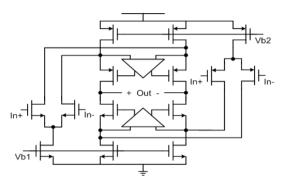

그림 2. SHA, MDAC의 연산 증폭기 구조 Fig. 2. Op-amp architecutre of SHA and MDAC

증폭기 내의 높은 귀환 요소를 가진다는 점이다. 또한 저전력을 소모하고, 높은 속도를 보장한다. 하지만 선형성이 줄어 드는 단점이 있다. 1.5비트로 구현된 스테이지는 선형성이 줄어드는 단점을 보완하고자 연산 증폭기에 이득 향상기를 추가 설계하여 선형성을 높일 수 있도록 하였다.

듀티 사이클 보정 회로는 클릭의 상승 에지와 하강에지 모두 사용하는 파이프라인 A/D 변환기의 입력 클럭 듀티 사이클에 무관하게 항상 50%의 듀티사이클을 가지는 클럭을 출력하게 보정해주는 역할을 한다. 온칩 기준 전류 발생기는 공정, 전원 전압, 온도에 관계없이 항상 일정한 기준전류를 얻을수 있으며, SHA 및 각각의 스테이지에 쓰이는 연산 증폭기의 바이어스 전류를 공급한다.

각각의 스테이지는 SHA, Sub-ADC, Sub-DAC, 잔류전압 증폭기(Residue Voltage Amplifier) 및 감 산기로 구성되어 있다. 일반적으로 마지막 세 개의 블록을 합쳐서 MDAC(Multiplying digital to analog converter)이라 한다. 본 논문에서는 잡음에 대한 영향을 최소화 하도록 모든 블록들을 완전 차 동 구조로 설계하였다.

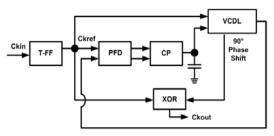

그림 3. 제안하는 듀티 사이클 보정 회로의 블록 다이어그램 Fig. 3. Block diagram of the proposed Duty-cycle Correction circuit

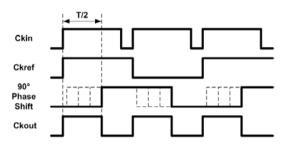

그림 4. 듀티 사이클 보정 회로의 타이밍 다이어그램 Fig. 4. Timing diagram of Duty-cycle Correction circuit.

또한 SHA와 MDAC의 연산 증폭기는 입력 전압의 범위 제한 문제를 해결하기 위해서 그림 2와 같이 NMOS와 PMOS로 입력 단을 구성하였다.

제안한 듀티 사이클 보정 회로의 블록 다이어그 램을 그림 3에 나타내었다.

제안한 듀티 사이클 보정 회로는 위상·주파수 검출기(Phase & Frequency Detector)<sup>[8]</sup>, 전하 펌프 (Charge Pump), 루프 필터(Loop Filter), 전압 제어 지연 회로(Voltage Controlled Delay Line)<sup>[9]</sup>로 이루어진 DLL 루프와 T-FF, XOR 게이트로 이루어져 있다.

제안하는 듀티 사이클 보정 회로의 타이밍 다이어그램은 그림 4에 나타내었다. T-FF는 입력 듀티사이클에 독립적인, 50%의 듀티 사이클을 가진 2T주기의 Ckref 신호를 만든다<sup>[10]</sup>. 또한 T-FF의 특성으로 인해 입력 듀티 사이클의 보정 범위를 최대화할 수 있다. 위상·주파수 검출기는 Ckref 신호와 전압 제어 지연 회로의 출력 신호를 입력으로 받는다. DLL 폐 루프가 잠금 상태일 때 전압 제어 지연 회로의 총 지연 시간이 한 사이클을 보장하기 때문에, 전압 제어 지연 회로에서 Ckref 신호 대비 90°의위상차를 가지는 신호를 얻을 수 있다.

Ckref 신호와 90°의 위상차를 가지는 신호를 XOR 게이트 입력으로 넣으면 입력 듀티 사이클에

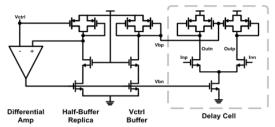

그림 5. 전압 제어 지연 회로

Fig. 5. Schematic of the Voltage controlled delay line

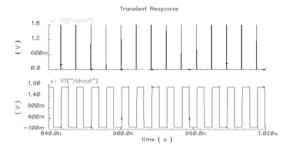

그림 6. 1%의 듀티 사이클을 가진 신호의 출력 파형 Fig. 6. Output waveform for a 1% duty cycle at 40MHz input clock

무관한 50%의 듀티 사이클을 가지는 Ckout 신호를 얻을 수 있다.

전원 전압에 대한 지터의 영향을 줄이기 위해 대 칭적인 부하를 갖는 지연 회로와 셀프 바이어싱 기법을 이용한 전압 제어 지연 회로를 그림 5에 나타내었다<sup>191</sup>. PMOS의 바이어스 전압 Vbp는 바이어스 회로의 입력인 Vctrl과 거의 같게 되므로, Vctrl 신호에 따라 버퍼의 실제 부하저항이 변하게 되어 버퍼의 출력신호의 스윙 폭을 변화시키고 버퍼의 지연을 조절할 수 있게 된다. 바이어스 회로는 차동증폭기와 하프 레플리카 회로를 이용해서 Vctrl 신호에 따라 버퍼 출력신호의 스윙 폭이 정해지도록 버퍼의 바이어스 전류를 제어한다.

차동 증폭기는 half-buffer replica 회로의 출력과 Vctrl 신호가 같아지는 Vbn 신호를 생성하므로, 만약 전원 전압이 변하여 Vctrl 신호가 같이 변하더라도 차동 증폭기의 (+) 노드를 Vctrl 신호와 같게 만들어서 같은 스윙 폭과 전류를 갖도록 Vbn 신호를 조절한다. 이렇게 함으로써 전원 전압의 변화에 상관없이 일정한 전류를 공급할 수 있게 된다. Vctrl 버퍼는 지연 단의 버퍼로부터 Vctrl 신호를 분리하여 커패시티브 커플링을 방지하는 역할을 한다.

제안하는 듀티 사이클 보정 회로에 입력 듀티 사이클이 1%인 신호가 들어왔을 때 과도기 응답 출

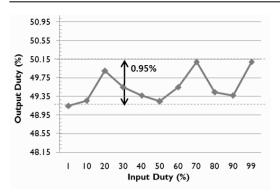

그림 7. 입력 듀티 사이클이 변화하였을 때 출력 듀티 사이 클의 변화

Fig. 7. Changes in the output duty cycle as a function of the input duty cycle

력 파형을 그림 6에 나타내었고, 입력 듀티 사이클 이 변화하였을 때 출력 듀티 사이클의 변화를 그림 7에 나타내었다.

모의 실험 결과, 제안하는 듀티 사이클 보정 회로는 입력 듀티 사이클이 1%에서 99%까지 변화하여도 0.95%의 변동을 가지는 50%의 듀티 사이클을 가진 출력 신호로 보정 가능하다.

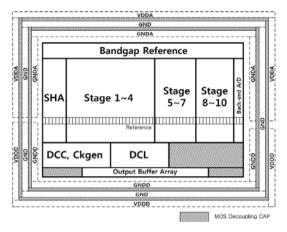

## Ⅲ. 12비트 A/D 변환기 레이이웃

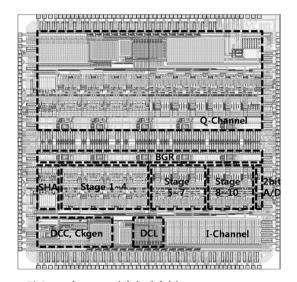

설계된 A/D 변환기는 무선랜 시스템에서 응용할수 있도록 전체적으로 I/Q 채널 A/D 변환기로 그림 8의 플로플랜과 같이 레이아웃 하였다.

I/Q 채널 A/D 변환기의 레이아웃은 아날로그 블록과 디지털 블록을 더블 가드 링을 만들어 분리하고, 레퍼런스 전압과 전원 전압에 바이패스 커패시터를 집적함으로써 잡음을 억제하였고, 선형성과 동적 성능을 향상시켰다. 또한 디지털 신호 라인과 아날로그 신호라인이 교차하는 부분은 그라운드 선을이용하여 신호간섭 현상을 제거하였다. 이와 같은 방법들을 토대로 레이아웃을 진행하였다. CMOS 0.18µm 1-poly 6-metal 공정을 이용하여 구현한 I/Q 채널 A/D 변환기의 레이아웃을 그림 9에 나타내었다[11].

레이아웃 결과 제작된 12비트 A/D 변환기의 유효 칩 면적은 12.92mm² (3.8mm x 3.4mm) 이다.

### Ⅳ. 측정 결과 및 고찰

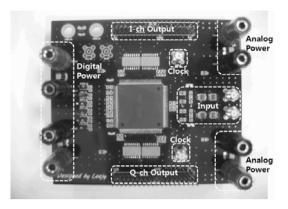

본 논문에서 구현된 A/D 변환기의 성능 측정을 위해서 그림 10과 같은 성능 검증용 PCB를 제작하

그림 8. 12비트 A/D 변환기 플로 플랜 Fig. 8. Floor-plan of 12 bits A/D converter

그림 9. 12비트 A/D 변환기 레이아웃 Fig. 9. Layout of 12 bits A/D converter

였다. I/Q 채널 A/D 변환기의 정합 특성을 고려하여 I-채널과 Q-채널을 대칭적으로 구성하였으며, 4층 기판을 사용하여 디지털 전원과 아날로그 전원을 분리하였다.

입력 단에는 신호 소스에서 나오는 하모닉을 제거하기 위해 대역 통과 필터 (Band-pass filter) 를 사용하였고, RF 트랜스포머를 이용하여 차동 신호로 변환시켜 주었다. 또한 트랜스포머 출력과 칩의 입력 사이에 직렬로 저항을 연결해 칩 내부의 SHA에서 생기는 스위칭 잡음이 아날로그 입력에 주는 영향을 최소화 하도록 하였다. 또한 출력 단에는 댐핑 저항을 사용해 과전류를 막아주고, RC 필터로서고주파 노이즈를 제거해 주었다.

그림 10. 12비트 A/D 변환기 성능 검증용 PCB Fig. 10. PCB picture for measurement of the 12bit A/D converter

그림 11. 12비트 A/D 변환기 측정 환경 Fig. 11. Measurement environment for 12bits A/D converter

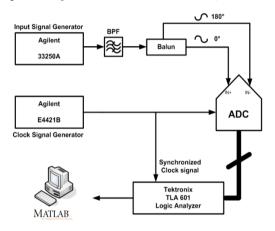

제작한 A/D 변환기의 측정 환경을 그림 11에 나타내었다. 아날로그와 디지털 전원을 분리하여 인가하였고, 지터 특성이 좋은 Agilent사의 파형 발생기(E4421B)에 의하여 클럭이 입력된다. 아날로그 입력은 하모닉 특성이 좋은 Agilent사의 신호 발생기(33250A)를 사용하였으며, 신호 발생기에서 생기는하모닉들을 추가적으로 제거해 주기 위해 대역 통과 필터 (Bandpass filter)를 사용하였다. A/D 변환기의 측정은 로직 분석기로 디지털 출력을 받아 매트랩 프로그램으로 분석하였다.

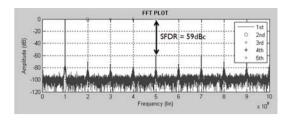

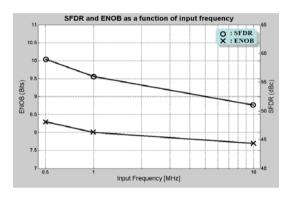

1MHz의 입력 주파수, 20MHz의 샘플링 속도에서 측정한 신호 스펙트럼을 그림 12에 나타내었다. 측정 결과 52dB의 SNDR, 59dBc의 SFDR을 얻었다. 입력 주파수를 1MHz에서 10MHz 까지 증가시킬 때 유효비트 및 SFDR을 나타낸 것을 그림 13에 나타내었다.

그림 12. 측정된 신호 스펙트럼 (Fs=20Mhz, Fin=1Mhz) Fig. 12. Measured signal spectrum (Fs=20Mhz, Fin=1Mhz)

그림 13. 입력 주파수에 따른 유효비트와 SFDR Fig. 13. Measured dynamic performance of ENOB and SFDR versus Fin

그림 14. 측정된 INL, DNL Fig. 14. Measured INL and DNL

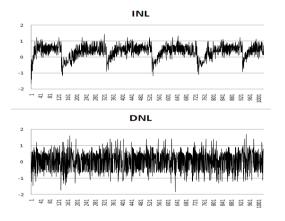

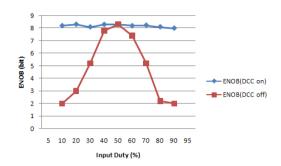

축정된 INL, DNL은 그림 14와 같이 각 각 +1.43LSB/-1.67LSB, +1.71LSB/-1.83LSB로 나타났다. 또한 입력 클럭의 듀티 사이클을 변화하였을 때, 전체 A/D 변환기의 성능 변화를 그림 15에 나타내었다. 제안하는 A/D 변환기의 측정 결과는 표 4에 요약하였다.

그림 15. 입력 클럭 듀티 사이클에 따른 유효비트 변화 Fig. 15. Variation in the ENOB as a function of input clock duty cycle

표 1. 제작된 A/D 변환기의 측정결과 요약 Table 1. Summary of measurement performances of the proposed ADC

|       | 모의실험 결과               | 측정 결과                 |

|-------|-----------------------|-----------------------|

| 변환 속도 | 40 MHz                | 20 MHz                |

| 공급 전원 | 1.8 V                 | 1.8 V                 |

| SFDR  | 79 dBc<br>(@Fin=1MHz) | 59 dBc<br>(@Fin=1MHz) |

| SNDR  | 71 dB<br>(@Fin=1MHz)  | 52 dB<br>(@Fin=1MHz)  |

| 전력 소모 | 199 mW                | 184 mW                |

| 공 정   | CMOS n-well 0.18um    |                       |

| 칩 면적  | -                     | 12.92 mm <sup>2</sup> |

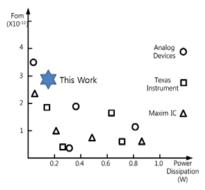

1.8V 단일 전원 전압에서 184mW의 전력을 소모하였고, CMOS n-well 0.18um 공정으로 제작한 칩의 유효 면적은 12.92 mm²를 나타내었다. 제안한 I/Q채널 12비트 A/D 변환기와 반도체 제조업체에서 제작한 상용 12비트 A/D 변환기의 성능을 비교하였다. 성능 비교 시 A/D 변환기의 주요 성능변수인 유효비트수(n)와 변환속도 및 전력소모를이용하여 (1)과 같은 FoM(Figure of Merit)을 이용하였다.

$$FoM = \frac{Power \ Dissipation}{2^{N} \times \ Sampling \ Frequency} [Joul/Hz]$$

(1)

상용 A/D 변환기와의 비교 분석결과는 그림 16 와 같다. 제안된 I/Q채널 12비트 A/D 변환기는 상 용제품과 비교 분석하여 보았을 때, 전력소모 측면 에서는 우수하였으나 변환속도가 다소 떨어지므로 구현된 변환기의 FoM이 중간 정도로 나타났다.

그림 16. 제안한 A/D변환기와 상용제품들과의 비교 Fig. 16. Comparison of FoM between the proposed A/D converter and commercial A/D converter

## Ⅳ. 결 론

본 논문에서는 무선 통신 분야 WLAN/WMAN 시스템에 적용되는 12비트 40MS/s A/D 변환기를 설계 및 구현하였다.

특히 스위치드 커패시터 기반의 파이프라인 구조의 A/D 변환기는 스테이지간 하나의 클럭과 그 반대 위상의 클럭을 쓰기 때문에, 칩 내에서 클럭의 정확한 50%의 듀티 사이클을 유지하기 위해 제안하는 듀티 사이클 보정 회로를 집적하였다. 이러한 듀티 보정 회로를 적용하였을 때, 입력 클럭 듀티 사이클이 변화하여도 전체 A/D 변환기의 성능의 변화는 5%내외로 안정적인 성능 변화를 나타내었다.

제안하는 A/D 변환기는 매그나 0.18um n-well 1-poly 6-metel CMOS 공정으로 제작되었으며, 측정 결과 1.8V 단일 전원 전압에서 전력 소모는 184mW, 1M의 입력 및 10M의 샘플링 속도에서 SNDR 및 SFDR이 각각 52dB 및 59dBc 수준을 보인다. 또한 제작된 A/D 변환기의 칩 면적은 12.92mm² 이다.

#### 참고문헌

- D. J. Johnston, and M. LaBrecque, "IEEE 802.16 WirelessMAN Specification Accelerates Wireless Broadband Access," Technology Intel magazine, August 2003.

- [2] L. Perraud, et al., "A Dual-Band 802.11 a/b/g Radio in 0.18um CMOS," IEEE ISSCC, Vol.47, pp.94-95, Feb. 2004.

- [3] S. Karthikeyan, "Clock duty cycle adjuster circuit for switched capacitor circuits," Electron.

- Lett., Vol.38. No.18, pp.1008-9, Aug. 2002.

- [4] J. Doyle, Y.J. Lee, Y.-B. Kim, H. Wilsch, and F. Lombardi, "A CMOS subbandgap reference circuit with 1-V power supply voltage,' IEEE J. Solid-State Circuits, Vol.39, No.1, pp.252 -255, Jan. 2004.

- [5] Lewis, S.H. and Gray, P.R., "A pipeline 5Msample/s 9bit analog-to-digital converter," IEEE JSSC, Vol.SC-22, pp.954-61, Dec. 1987.

- [6] B. Song, S. Lee and M. F. Tompsett, "A 10-b 15-MHz CMOS Recycling Two-Step A/D Converter," IEEE J. Solid-State Circuits, Vol.25, No.6, pp.1328-1338, Dec. 1990.

- [7] C. R. Grace, P. J. Hurst and Stephen H. Lewis, "A 12-bit 80-MSample/s Pipelined ADC With Bootstrapped Digital Calibration," IEEE J. Solid-State Circuits, Vol.40, No.5, pp.1038-46, May. 2005.

- [8] Sungjoon Kim, "A 960-Mb/s/pin Interface for Skew-Tolerant Bus Using Low Jitter PLL," IEEE J. Solid-State Circuits, Vol.32, No.5, pp.691 - 700, May. 1997.

- [9] J. G. Maneatis, "Low-jitter process-independent DLL and PLL based on self-biased techniques," IEEE J. Solid-State Circuits, Vol.31, pp.1723 --1732, Nov. 1996.

- [10] J.N. Jang and H.J. Park, "An All-Digital CMOS Duty Cycle Correction Circuit with a duty cycle correction range of 15-to-85% for multi-phase applications," IEICE TRANS. Electron., Vol.E88-C, No.4, pp.773-7, Apr. 2005.

- [11] B. Min, Y. Cho, H. Chae, H. Park and S. Lee, "A 10b 100MS/s 1.4mm2 56mW 0.18um CMOS A/D Converter with 3-D Fully Symmetrical Capacitors," IEICE Trans. on Electronics, Vol.E89-C, No.5, pp.630-635, May 2006.

#### 이 재 용(Jae-yong Lee)

99

2006년 2월 인하대학교 전자 공 학과 졸업

정회원

2008년 2월 인하대학교 전자 공 학과 석사 졸업

2008년 2월~현재 페어차일드 코 리아 반도체 주식회사 연구원 <관심분야> 아날로그 VLSI 설계,

파이프라인 A/D 변환기 설계

#### 조 성 일(Sung-il Cho)

2006년 2월 수원대학교 정보통신 공학과 졸업

2006년 9월~현재 인하대학교 전 자공학과 석사과정

<관심분야> 아날로그 VLSI 설계, 파이프라인 A/D 변환기 설계

## 박 현 묵(Hyun-mook Park)

준회워

2007년 8월 인하대학교 전자 공 학과 졸업

2007년 9월~현재 인하대학교 전 자공학과 석사과정

<관심분야> 아날로그 VLSI 설계, 파이프라인 A/D 변환기 설계

## 이 상 민(Sang-min Lee)

정회원

1987년 인하대학교 전자 학사졸업 1989년 인하대학교 전자공학 (정보공학) 석사 2000년 인하대학교 전자공학 (정보공학) 박사

1989년 1월~1994년 7월 (주)LG 이노텍 중앙연구소 연구원 선 임 연구원

1995년 1월~2002년 3월 (주)삼성전자 삼성종합기술원 연구원 책임 연구원

2004년 4월~2005년 2월 한양대학교 의과대학 의공학 교실 연구교수

2005년 3월~2006년 8월 전북대학교 공과대학 생체정 보공학부 조교수

2006년 9월~현재 인하대학교 공과대학 전자전기공학 부 조교수

<관심분야> Healthcare system design, Psycho-acoustics, brain-machine interface

## 윤 광 섭(Kwang-sub Yoon)

정회원

1982년 2월 인하대학교 전자 공학과 졸업 1983년 2월 Georgia Institute Inc, Technology 전자공학 석사 졸업 1989년 2월 Georgia Institute Inc, Technology 전자공학 박사 졸업 1984년 3월~1989년 2월 Georgia

Institute of Technology Research Assistant 1989년 3월~1992년 2월 Silicon Systems Inc, Tustin Calif. U.S.A Senior Design Engineer 1992년 3월~현재 인하대학교 전자공학과 교수 <관심분야> 혼성신호처리 집적회로 설계, 설계 자동화 및 소자/회로/시스템 모델링 등