# MB-OFDM 방식 UWB 모뎀의 SoC칩 설계

정회원 김도훈\*, 이 현 석\*, 조진 웅\*, 서 경 학\*

## MB-OFDM UWB modem SoC design

Do-hoon Kim\*, Hyeon-seok Lee\*, Jin-woong Cho\*, Kyeung-hak Seo\* Regular Members

요 약

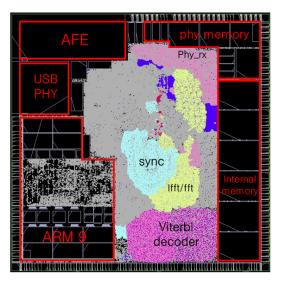

본 논문은 고속 무선 통신을 위한 모뎀 설계에 관한 것이다. 고속 통신을 위한 기술에는 여러 가지가 있는데, 그 중 넓은 주파수를 사용하고 여타 서비스에 주파수 간섭을 일으키지 않는 기술인 MB-OFDM (Multi-Band Orthogonal Frequency Division Multiplexing) 방식의 UWB (Ultra-Wideband) 모뎀의 SoC (System-on-Chip) 칩을 설계하였다. 개발된 모뎀 SoC 칩의 기저대역 시스템은 WiMedia에서 정의한 표준안을 따라서 설계되었다. 설계된 SoC 칩은 코어 부분인 FFT/IFFT (Fast Fourier Transform/Inverse Fast Fourier Transform), 송신부, 심볼동기 및 주파수 오프셋 추정부, 비터비 디코더, 그리고 기타 수신부등으로 구성되어 있다. 반도체 공정은 90nm CMOS (Complementary Metal-Oxide-Semiconductor) 공정을 사용하였고, 칩 사이즈는 약 5mm x 5mm 이다. 2009년 7월 20일에 fab-out되었다.

**Key Words**: UWB. SoC. MB-OFDM. FFT/IFFT. synchronization. CMOS

#### **ABSTRACT**

This paper presents a modem chip design for high-speed wireless communications. Among the high-speed communication technologies, we design the UWB (Ultra-Wideband) modem SoC (System-on-Chip) Chip based on a MB-OFDM scheme which uses wide frequency band and gives low frequency interference to other communication services. The baseband system of the modem SoC chip is designed according to the standard document published by WiMedia. The SoC chip consists of FFT/IFFT (Fast Fourier Transform/Inverse Fast Fourier Transform), transmitter, receiver, symbol synchronizer, frequency offset estimator, Viterbi decoder, and other receiving parts. The chip is designed using 90nm CMOS (Complementary Metal-Oxide-Semiconductor) procedure. The chip size is about 5mm x 5mm and was fab-out in July 20th, 2009.

#### I. 서 론

최근 컴퓨터 기술의 급속한 발전으로 인해 기존의 텍스트 위주의 사용자 환경에서 벗어나 이미지, 그래픽, 오디오 및 비디오 데이터 등을 제공하는 멀 티미디어 사용자 환경으로 변화하고 있다.

최근 들어 통신, 방송을 중심으로 한 다양한 신 규 무선 기술이 개발되어 서비스가 도입되고, 각종 산업에서 무선 서비스에 대한 수요가 급격히 확대 됨에 따라 주파수에 대한 수요가 폭발적으로 증가 하고 있는 상황이다.

UWB(Ultra-Wideband)는 낮은 전력으로 초고속 통신을 실현하는 근거리 무선통신기술로써 이러한 주파수 부족 현상을 넘어서서 신규 기술을 도입할 수 있는 획기적인 기술방식이다. UWB는 대역별로 배타적 주파수 이용권한이 부여되는 방식을 탈피하 여, 매우 넓은 주파수 대역을 활용하면서도 기존에 해당 주파수를 사용하고 있는 여타 서비스에 주파

<sup>\*</sup> 전자부품연구원 통신네트워크센터 ({speedo, hslee, chojw, paul\_kseo}@keti.re.kr) 논문번호: KICS2009-07-270, 접수일자: 2009년 7월 27일, 최종논문접수일자: 2009년 08월 05일

수 간섭을 일으키지 않는 기술방식이면서 동시에 수백 Mbps 이상의 데이터 전송률을 실현할 수 있다.

UWB 전송방식 중의 하나인 MB-OFDM(Multi-Band Orthogonal Frequency Division Multiplexing) 시스템은 앞서 설명한 전송 특성을 만족하는 시스템으로써 사무실이나 가정과 같은 작은 공간에서 10m정도의 근거리에 있는 DVD 플레이어, MP3 플레이어, PC, TV, PMP, 디지털 카메라, 프린터 등을 연결하는 무선 근거리 통신 기술로 개발이 활발히 진행되고 있다<sup>[1]</sup>.

본 논문에서는 MB-OFDM 방식의 UWB 모템을 설계하고 SoC로 구현한 결과를 소개하고 있다. 개발된 모뎀 SoC 칩의 기저대역 시스템은 WiMedia에서 정의한 표준안을 따라서 설계되었다. 설계된 SoC 칩은 코어 부분인 FFT/IFFT (Fast Fourier Transform/Inverse Fast Fourier Transform), 송신부, 심볼동기 및 주파수 오프셋 추정부, 비터비 디코더, 그리고 기타 수신부등으로 구성되어 있다. 반도체 공정은 90nm CMOS (Complementary Metal-Oxide -Semiconductor) 공정을 사용하였고, 칩 사이즈는약 5mm x 5mm이다. 본 논문에서 설계과정 및 결과는 UWB 모뎀을 설계하려는 산업체의 설계 기초자료로 활용될 수 있다.

본 논문은 다음과 같이 구성되어 있다. 먼저 2장에서는 UWB 모뎀 SoC 설계 과정을 설명한다. 그리고 3장에서는 SoC 설계 결과를 설명한다. 그리고 4장에서는 본 논문의 결론을 맺는다.

#### Ⅱ. SoC 설계

모뎀 부분은 WiMedia 표준안에 따라서 설계된 MAC/PHY (Media Access Control Layer/Physical Layer)와 AFE (Analog-Front-End) 부분으로 나눌수 있다.

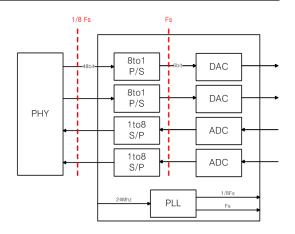

그림 1에 나타나 있는 AFE는 RF (Radio Frequency) 로부터 아날로그 I/Q (Inphase/ Quadrature Phase) 신호를 받거나 RF로 I/Q 신호를 보내는 고속 ADC/DAC (Analog-to-Digital Converter / Digitalto-Analog Converter)와 고속 신호를 병렬화 하는 S/P (Serial-to-Parallel), P/S (Parallel-to-Serial) 블록 으로 구성된다.

모뎀부분은 ADC/DAC 샘플링 주파수의 1/8배 클럭으로 동작을 하기 때문에 고속 데이터를 병렬 화하는 S/P, P/S가 AFE에 사용된다. PLL (Phase Locked Loop)은 24Mhz의 클럭을 입력받아 AFE에

그림 1. AFE(Analog-Front-End) 구조

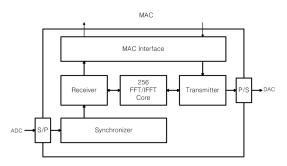

그림 2. PHY 블록

서 사용되는 샘플링 클럭 (Fs)과 디지털 회로를 동작시키는 기본 주파수 (Fs/8)를 발생시킨다.

디지털 회로의 대부분을 차지하는 PHY블록은 다음과 같은 형태로 구성되어 있다. 코어 블록인 IFFT/FFT는 256 포인트로 구현되어 있으며 핵심 연산부는 Radix-4 형태로 구현을 하였다. 본 모뎀은 송신과 수신이 동시에 이루어지는 형태가 아니므로 1개의 블록으로 송수신 동작형태에 따라서 FFT 또는 IFFT로 동작하게 된다.

송신부는 송신데이터를 스크램블하고 컨볼루션 인코더를 통과한 후 전송모드에 따라서 평쳐링 (Puncturing) 과정을 거친다. 그 후 인터리버를 거치 고 QPSK (Quadrature Phase Shift Keying) 또는 DCM (Dual Carrier Modulation) 기법으로 변조된 다. 변조된 심볼은 IFFT를 통과하여 AFE단으로 전 송된다.

전송패킷에서 헤더부분은 오류 보상을 위해서 RS (Reed-Solomon) 부호화 기법 [2]이 적용되고, 페이로드 부분은 적용되지 않는다. 송신부는 병렬 구현을 하였음에도 불구하고 면적 측면에서 전체 모뎀

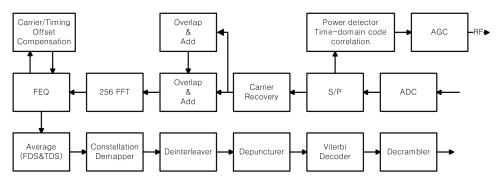

그림 3. 수신기 구조

부분의 약 5%를 넘지 않을 정도로 작고 구현도 쉬운 편이다. 전송 모드별로 TDS (Time Domain Spreading) 및 FDS (Frequency Domain Spreading) 이득을 얻을 수 있는데, 송신부에서는 간단하게 위의 기능을 구현할 수 있다.

송신부의 최종 데이터는 6비트 DAC에 최적화되도록 IFFT 출력값을 조정할 필요가 있으며, 오버플로우가 발생하지 않도록 디지털 회로의 마지막 단에서 주의를 해야한다. OFDM 신호의 특성상 6 비트 범위를 넘어서는 값을 가지는 신호가 종종 발생할 수 있는데, 시스템 전체의 성능을 고려하여 클리핑 범위를 조절하는 것이 필수적이다. 수신부는 모뎀 사이즈의 절반 이상을 차지하는 큰 블록이다. 특히 비터비 디코더는 4 비트 입력 구조로 되어 있어코어 블럭인 IFFT/FFT 보다도 더 크고, 나머지 디코딩 블록도 병렬 구조로 구현이 되어 모뎀 면적과전력 소모 증가에 많은 영향을 미친다.

수신데이터는 S/P 블록을 통과하여 DFE (Digital-Front-End)로 입력된다. 입력된 데이터를 이용하여 패킷 검출 회로는 대략적인 심볼의 위치를 찾게 되고, 이를 바탕으로 AGC (Auto Gain Control)을 수 행한다. AGC가 완료된 데이터는 수신기가 오버플로우를 발생시키지 않고 올바르게 동작할 수 있는 상태가 된다.

이후 심볼 동기회로와 RF단에서 발생한 캐리어 오프셋을 보상하는 회로가 동작한다. 이 회로를 구 성하기 위해서는 복잡한 복소수 곱셈기가 필요한데, 초기화 과정에서 동시에 동작하는 구간이 없기 때 문에 블록을 공유하도록 설계하여 회로 크기를 많 이 줄일 수 있었다.

심볼 동기회로는 프리앰블데이터와 수신데이터의 상관관계를 계산하여 최고값을 찾는 형태로 동작한 다<sup>[3]</sup>. 이 회로는 병렬로 입력되는 데이터를 매 클럭 마다 곱셈기 및 덧셈기를 동작시켜야 하기 때문에 매우 복잡하게 구현될 수 있다. 따라서 곱셈기의 사용을 최대한 억제하고, 다양한 채널 환경에서 심볼 동기 회로가 잘 동작할수 있는 범위내에서 심볼동기를 위한 데이터의 개수도 최소화하였다.

프리앰블 데이터는 초기 24개의 심볼은 TFC1-10 에 해당하는 10개의 시퀀스이다. 이 시퀀스는 시간 축에서의 최대값이 클리핑이 생기지 않도록 적당하게 선택된 값이며, 심볼동기에 사용이 된다. 설계된 모뎀에서는 오버 샘플링이 적용되어 표준안에서 제안된 128개의 값보다 2배 많은 256개의 값이 사용이 되었는데, 심볼동기회로의 복잡도를 줄이기 위해이중 절반인 128개만이 사용되었다. PHY단에서는 TFC값에 따른 시퀀스를 모두 가지고 있고, MAC에서 내려온 정보에 따라서 특정 TFC에 해당하는 시퀀스로 패킷 검출 및 심볼 동기과정을 수행하게 된다.

캐리어 오프셋 추정 및 보상 회로는 수신데이터의 자기 상관치를 이용하여 오프셋을 추정한 다음역 탄젠트 (arctan) 회로를 이용하여 위상을 계산하여 S/P 블록 뒤에서 바로 보상하는 구조로 되어 있다. 사용되는 샘플 개수는 시스템의 복잡도와 성능을 고려하여 결정되었다. 이때 사용되는 복소곱셈기는 AGC에서 사용되는 것과 같은 구조이기 때문에 동작시간의 차이에 의해 서로 공유할 수 있도록 설계되었다. 이러한 보상후에 남아 있는 캐리어 오프셋은 FEQ (Frequency Equalizer) 뒤에서 다시 한번 잔류 오프셋 추정/보상을 하도록 하였다.

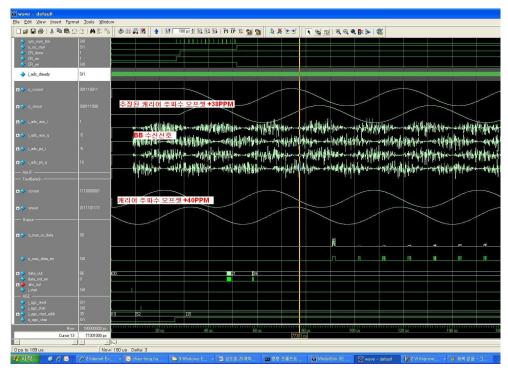

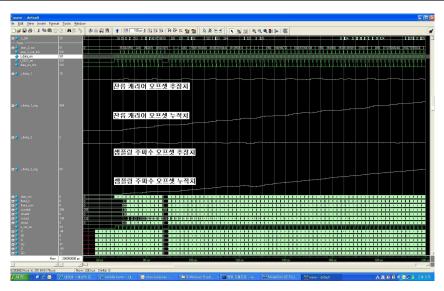

그림 4는 설계된 verilog 코드의 시뮬레이션 결과를 보여준다. 각각 +40ppm의 캐리어 주파수오프셋과 샘플링 주파수 오프셋이 존재하는 상황에서 초기 캐리어 주파수 오프셋을 추정하고 보상하는 결과를 보여준다. 실제 주파수 오프셋은 +40ppm인데

추정된 오프셋은 +38ppm으로 추정값과 실제 오

그림 4. 초기 캐리어 오프셋 추정 시뮬레이션 결과

프셋의 차이가 크지 않음을 알 수 다. 실제 오프셋과 추정 오프셋의 차이 +2ppm은 FEQ뒤에서 한번 더 잔여 오프셋을 추정하여 보상하게 된다.

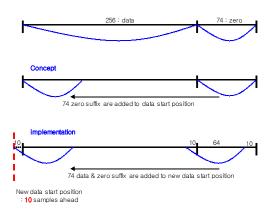

FFT에 입력되는 데이터는 Zero-suffix구간을 고려하여 overlap & add 과정을 필요로 한다. 이때, ADC의 샘플링 타이밍 오프셋(+-20ppm)을 고려하여 정확한 심볼의 시작지점보다 몇 샘플 더 앞을 심볼의 시작점으로 선택하여 FFT를 수행하도록 설계하였고 시작지점은 소프트웨어로 제어가 가능하도록 되어있다.

그림 5. Zero-suffix구간의 Overlap & Add 개념도

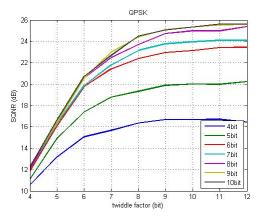

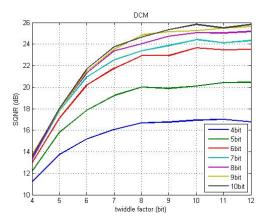

아래의 그림은 FFT의 fix-point시뮬레이션 결과를 보여준다. QPSK와 DCM 모드에 따라서 각각 시뮬 레이션을 했으며, FFT의 twiddle factor와 각 단에 서의 버터플라이 연산후의 데이터 비트의 크기에 따른 FFT의 SQNR (Signal to Quantization Noise Ratio)를 계산하였다. 그림 6은 QPSK 모드에서의 결과이고, 그림 7은 DCM모드에서의 시뮬레이션 결 과이다.

가로축은 FFT의 twiddle factor의 비트수이고, 세 로축 SQNR은 dB 단위로 표시하였다. 시뮬레이션

그림 6. QPSK 모드에서의 FFT 시뮬레이션 결과

그림 7. DCM 모드에서의 FFT 시뮬레이션 결과

을 통해서 twiddle factor는 최소 8bit 이상이 필요하고 10bit 이상이 되면 최적의 성능을 얻을 수 있음을 확인할 수 있다. 버터플라이 연산후의 데이터비트 8bit 이상이 되면 24dB 이상의 SQNR을 얻을수 있다.

그림 7은 DCM 모드에서의 FFT 시뮬레이션 결과이다. DCM모드의 결과도 QPSK모드에서와 비슷하다. 다만 DCM 모드는 16 QAM의 레벨을 가지기 때문에 FFT입력 비트의 크기 및 버터플라이 연산후의 크기 조정이 최적화 되어야만 SQNR 성능의 저하가 생기지 않는다.

FEQ는 FFT를 통과한 데이터에서 채널 왜곡부분을 보상하도록 1-tap으로 구현되었다. MB-OFDM UWB는 주파수 호평 방식 [4]도 포함이 되어 있기때문에 주파수별 채널 왜곡을 각각 보상할 수 있도록 그림 8처럼 설계되었고, 채널추정은 식(1)에 따라서 계산된다. 나눗셈은 하드웨어 사이즈를 간략하게 할 수 있도록 개발된 알고리즘을 사용하였다.

$$Y = X \times H \quad (H = h_i + jh_j , X = x_i + jx_j , Y = y_i + jy_j)$$

$$1/H = X/Y = (X \times Y^*)/(Y \times Y^*) = (X \times Y^*)/|Y|^2$$

$$= (x_i + jx_j) \times (y_i - jy_j)/(y_i^2 + y_j^2)$$

$$= (x_i y_i + x_j y_j)/(y_i^2 + y_j^2) + j(x_j y_i - x_i y_j)/(y_i^2 + y_j^2)$$

(1)

그림 8. FEQ 초기 채널 추정 구조

표 1. TFC와 프리앰플 패턴

| TFC No. | Base seq./<br>Preamble | E | BANI | )_ID | fo | r TF | C |

|---------|------------------------|---|------|------|----|------|---|

| 1       | 1                      | 1 | 2    | 3    | 1  | 2    | 3 |

| 2       | 2                      | 1 | 3    | 2    | 1  | 3    | 2 |

| 3       | 3                      | 1 | 1    | 2    | 2  | 3    | 3 |

| 4       | 4                      | 1 | 1    | 3    | 3  | 2    | 2 |

| 5       | 5                      | 1 | 1    | 1    | 1  | 1    | 1 |

| 6       | 6                      | 2 | 2    | 2    | 2  | 2    | 2 |

| 7       | 7                      | 3 | 3    | 3    | 3  | 3    | 3 |

| 8       | 8                      | 1 | 2    | 1    | 2  | 1    | 2 |

| 9       | 9                      | 1 | 3    | 1    | 3  | 1    | 3 |

| 10      | 10                     | 2 | 3    | 2    | 3  | 2    | 3 |

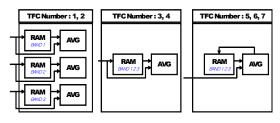

TFC1, 2의 경우는 주파수 호핑 패턴상 수신데이터를 3심볼구간 동안 저장하는 메모리가 필요하게되고, TFC 3, 4의 경우는 필요한 메모리가 TFC5, 6, 7처럼 1심볼구간만 필요하다. 따라서 동일 밴드그룹 내에서 3개의 밴드에 대해서 각각의 채널 추정이 가능하도록 FEQ블록이 설계되어 있다. 평균을취하는 블록이 들어간 것은 프리앰블의 채널 추정시퀀스가 동일한 심볼의 연속으로 구성이 되어 있어서 평균값 계산을 통한 오차를 줄이기 위함이다.

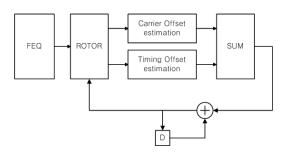

FEQ에서 출력된 데이터는 잔류 캐리어 오프셋 및 샘플링 주파수 오프셋을 보상하는 회로를 거친다. 이는 OFDM 방식의 특성상 오프셋이 크지 않을 경우 시간축상에서 위의 오프셋을 보상하는 방법보다는 주파수상에서 오프셋을 보상하는 방법이성능상에 잇점이 있기 때문에 이런 형태로 구현하였다.

UWB에서는 특정 서브캐리어에 파일럿 신호를 할당하도록 되어 있어서 수신단에서 파일럿 신호의 위상 변화 정도를 측정하여 주파수 오프셋을 계산 하였다.

아래 그림 9는 잔여 캐리어 오프셋을 추정하고 샘플링 주파수 오프셋을 추정하여 이를 합산한 값 을 누적한 후 피드백시키는 알고리즘을 보여준다 [4-[5]. 특히 샘플링 주파수 오프셋은 서브 캐리어 번

그림 9. 주파수 오프셋 보상 회로

그림 10. 잔류 캐리어 주파수 오프셋과 샘플링 주파수 오프셋 보상 회로의 시뮬레이션 결과

호가 클수록 번호에 비례해서 영향을 주기 때문에 주파수가 높은 서브캐리어에 영향을 많이 주게 되 어서, 이를 보상해주지 않으면 시스템의 성능에 많 은 영향을 주게 된다.

위의 그림 10은 잔류 캐리어 오프셋 주파수 추정 회로와 샘플링 주파수 오프셋 추정 회로의 시뮬레 이션 결과를 보여준다. 설계된 verilog코드는 각각 +40ppm의 주파수 오프셋이 있는 환경에 동작하고 있으며 초기 캐리어 주파수 오프셋이 추정 및 보상 된 후 약 1~2ppm의 잔류 캐리어 주파수 오프셋과 +40ppm의 샘플링 주파수 오프셋이 있는 상황에서 설계된 회로가 정상적으로 동작하고 있음을 보여주 고 있다. 각각의 주파수 오프셋이 양수이기 때문에 추정된 에러는 0에 근접한 일정한 값이고, 누적치는 시간의 흐름에 대해서 계속 증가하여 주파수 오프 셋을 따라 가고 있음을 알 수 있다. 본 설계에서는 추정된 값이 누적할 때 적당량 크기를 조절하기 때 문에 누적치가 일정한 선형이 되도록 하였다. 그렇 지 않으면 누적치가 출렁거리게 되어 성능에 영향 을 줄 가능성이 크게 된다.

주파수 오프셋이 보상된 데이터는 QPSK또는 DCM 디매퍼를 통과한 후 비터비 디코더를 거쳐 최종 데이터가 MAC/PHY 인터페이스를 통해서 MAC 단으로 올라가게 된다.

비터비 디코더는 200Mbps 데이터 모드까지 지원 할 경우 2bit 데이터 입력형태(Radix-4)로 구현할 수 있는데, 480Mbps DCM 모드를 지원하기 위해 서는 4bit 데이터 입력형태(Radix-16)로 병렬화된

표 2. 비터비 디코더의 입력 데이터에 따른 동작 클릭 비교

| Data rate (Mbps) | Min. clock<br>(Mhz) | Min. clock<br>(Radix-4) | Min. clock<br>(Radix-16) |

|------------------|---------------------|-------------------------|--------------------------|

| 53.3             | 53.3                | 27.5                    | 13.8                     |

| 80               | 80                  | 40                      | 20                       |

| 106.7            | 106.7               | 53.3                    | 26.7                     |

| 160              | 160                 | 80                      | 40                       |

| 200              | 200                 | 100                     | 50                       |

| 320              | 320                 | 160                     | 80                       |

| 400              | 400                 | 200                     | 100                      |

| 480              | 480                 | 240                     | 120                      |

구조로 구현이 되어야 한다. 따라서 하드웨어 사이 즈가 매우 커지게 된다. 사이즈를 줄이기 위해서는 기본동작주파수를 2배로 키우면 2bit데이터를 입력 받는 형태로 바꿀 수 있지만 이럴 경우 하드웨어의 동작주파수가 너무 높아져서 구현이 쉽지 않을 뿐만 아니라 파워소모측면에서도 좋지 않을 것으로 예상된다.

#### Ⅲ. SoC 설계 결과

본 설계를 통한 회로는 90nm CMOS 공정으로 제작되었다. 사이즈의 최적화를 위해서 dual port 메모리의 경우 256byte를 넘지 않으면 register로 구현을 하고 그 이상의 경우는 메모리 셀을 사용하여 구현하였다. 모뎀 파트는 전체 칩의 약 1/2이하를 차지하며, standard cell 대부분을 사용한다. 칩 사이즈는 약 5mm x 5mm이고, gate count는 모뎀파트

그림 11. 설계된 UWB 칩

만 160만 gate이다. 모뎀 디버깅과 소프트웨어를 위한 내부 메모리를 충분히 사용하였고, USB 2.0 과 SDIO 인터페이스를 지원하고 있다.

MB-OFDM UWB 모뎀은 고속의 데이터를 전송하기 때문에 높은 시스템 동작 주파수를 요구한다. 현실적으로 타당한 베이스밴드 동작 주파수는 ADC/DAC의 샘플링 주파스의 몇 분의 1 수준이기에 이에 해당하는 만큼 병렬 구조로 내부를 설계해야 한다. 따라서 칩 면적도 많이 커지게 되고 알고리즘에비해서 실제 verilog 설계 방법이 매우 복잡해지는 경우가 많았다.

90nm 공정을 사용했지만 layout상에서 타이밍이 잘 나오지 않는 부분이 몇 부분이 있었고, 이를 극복하기 위해서 합성 툴에서 최적화를 여러 번 수행하였다.

### V. 결 론

본 논문에서는 MB-OFDM 방식의 UWB 모뎀의 SoC 칩을 설계하였다. 개발된 모뎀 SoC 칩의 기저 대역 시스템은 WiMedia에서 정의한 표준안을 따라서 설계하였다. 설계된 SoC는 2009년 3월30일에 fab-in되어 7월 20일에 fab-out되었다. 현재 공정기술의 진화에 따라서 65nm 또는 45nm의 fab을 적용할 필요가 있다. 그리고 시장 경쟁력 확보를 위해서는 RF와 원 칩화된 형태로 구현이 필요하고, Wireless USB와 블루투스 기능과의 결합도 필수적일 것으로 예상된다.

#### 참 고 문 헌

- ECMA International, Standard ECMA-368, "High rate ultra wideband PHY and MAC standard," December 2007.

- [2] J. G. Proakis, "Digital Communications, 4th ed". New York: McGraw-Hill, 2001.

- [3] J. Terry and J. heiskala, "OFDM Wireless LANs: A Theoretical and Practical Guide", SAMS, 2002.

- [4] A. Batra et al., "Design of a multiband OFDM system for realistic UWB channel environments," *IEEE Trans. Microw. Theory Tech.*, Vol. 52, No. 9, pp. 2123 2138, Sep. 2004.

- [5] B. Sahu, D. Sen, R. V. Kumar, and S. Chakrabrti, "A Frequency Offset Estimation Scheme for OFDM Based UWB Systems," in *Proc. IEEE TENCON* 2006, pp. 1-4, Nov. 2006.

- (6) S.W.Choi, S.S.Choi, "200Mbps Viterbi decoder for UWB", ICACT 2005, pp. 904-907.

- [7] C. F. Liang, S. I. Liu, Y. H. Chen, T. Y. Yang, and G. K. Ma, "A 14-band Frequency Synthesizer for MB-OFDM UWB Application," in Proc. IEEE ISSCC 2006, pp 428-437, Feb. 2006.

- [8] A. Batra, J. Balakrishnan, G. R. Aiello, J. R. Foerster, and A. Dabak, "Design of a multiband OFDM system for realistic UWB channel environment," *IEEE Trans. Microw. Techn.*, Vol. 52, No. 9, pp. 2123 138, Sep. 2004.

- [9] 김정주, 왕우봉, 장경희, "UWB MB-OFDM 시스템을 위한 심볼 타이밍및 반송파주파수 오프셋 추정 기법," 한국통신학회논문지, Vol. 31, No. 3A, pp. 232-239, Mar. 2006.

- [10] J. R. Foerster, et al., "Channel modeling subcommittee report final," IEEE P802.15 Working Group for Wireless Personal Area Networks (WPANs). Feb. 2003.

#### 김 도 훈 (Do-hoon Kim)

정회원

1998년 포항공과대학교 전자·전 기공학과(학사)

2000년 포항공과대학교 전자·전 기공학과(석사)

2000년-2005년 (주)LG전자 선 임연구원

2005년~현재 전자부품연구원

통신네트워크연구센터 선임연구원 <관심분야> WPAN, UWB 모뎀

## 조 진 웅 (Jin-woong Cho)

정회원

1986년 광운대학교 전자통신 공학과(학사)

1988년 광운대학교 전자통신 공학과(석사)

2001년 광운대학교 전자통신 공학과(박사)

1989년~1993년 동양정밀 중

앙연구소 / 주임연구원 1993년~현재 전자부품연구원 통신네트워크연구센터 / 수석연구원 <관심분야> 무선통신, WPAN

### 이 현 석 (Hyeon-seok Lee)

정회원

2000년 한양대학교 전자통신·전 파공학과 (학사)

2002년 한양대학교 전자통신·전 파공학과 (석사)

2002년-2003년 (주)삼성전기 무 선랜AP 선행개발 / 주임연구원 2003년~현재 전자부품연구원 통

신네트워크연구센터 선임연구원 <관심분야> 무선통신MAC, 무선보안

#### 서 경 학 (Kyeung-hak Seo)

정회원

1978년 서울대학교 전자공학과 (학사)

1980년 KAIST 전자공학과(석사) 1989년 SYRACUSE대학 공과 대학원(박사)

1980년~2001년 삼성전자 Personal Multimedia 사업팀장

2001년~현재 전자부품연구원 정보통신미디어연구본 부장

<관심분야> 무선통신, WPAN