# TWDM-PON 응용을 위한 4×10 Gb/s Transimpedance Amplifier 어레이 설계 및 구현

양 충 열', 이 강 윤', 이 상 수'

# A Design and Implementation of 4×10 Gb/s Transimpedance Amplifiers (TIA) Array for TWDM-PON

Choong-reol Yang, Kang-yoon Lee, Sang-soo Lee

요 약

TWDM-PON 시스템 수신부에 사용될 4×10 Gb/s Transimpedance Amplifier (TIA) 어레이가 0.13 μm CMOS 기술로 구현하였다. TIA의 대역폭 향상을 위하여 인덕터 피킹 기술과 1.2 V 기반의 저전압 설계기술을 제안한다. 0.5 pF PD 용량에서 7 GHz 3 dB 대역폭을 구현한다. 1.2V 공급에서 채널당 31 mW를 소모하는 동안 Trans-resistance gain 은 71.81 dB♀이다. TIA의 입력 감도는 -33.62 dBm를 갖는다. 4 채널을 포함하는 전체 칩크기는 1.9 mm × 2.2 mm 이다.

Key Words: TWDM-PON, Optical Transceiver, CMOS, Transimpedance Amplifier, TIA, Array

#### **ABSTRACT**

A  $4\times10$  Gb/s Transimpedance Amplifier (TIA) array is implemented in 0.13  $\mu m$  CMOS process technology, which will be used in the receiver of TWDM-PON system. A technology for bandwidth enhancement of a given  $4\times10$  Gb/s TIA presented under inductor peaking technology and a single 1.2V power supply based low voltage design technology. It achieves 3 dB bandwidth of 7 GHz in the presence of a 0.5 pF photodiode capacitance. The trans-resistance gain is 50 dB $\Omega$ , while 48 mW/ 1channel from a 1.2 V supply. The input sensitivity of the TIA is -27 dBm. The chip size is 1.9 mm  $\times$  2.2 mm.

# I. 서 론

TWDM-PON 기술은 PtP 구조를 갖고 광역 액세 스, 광대역 서비스를 바탕으로 일반주거 가입자, 비즈 니스 가입자 등에 적용되며, WDM-PON 시스템을 OLT에 적용하기 위해서는 저가형 파장가변 광원 및 이를 이용한 파장가변 트랜시버 개발이 요구된다. WDM-PON을 상용화하는데 가장 큰 장애요인은 저가화 문제이다. 이를 해결하기 위해서는 집적화가 필수적으로 요구되는데 대부분의 고속 Data rate를 갖는 TIA는 BJT 공정이나, SiGe로 구현되고 있으나 본 논문에서는 CMOS 기술을 이용하여 OLT 장비의 광송수신 모듈을 단일 칩으로 만들어 저가화, 소형화, 저전력화를 이루고, 라인카드 제작 단가를 낮추는 것이

<sup>※</sup> 본 연구는 미래창조과학부가 지원한 2014년 정보통신 방송(ICT) 연구개발 사업의 연구결과로 수행되었음. (14-000-05-002)

<sup>•</sup> First Author: ETRI Optical Internet Research Department Optical Access Laboratory, cryang@etri.re.kr, 정회원

<sup>°</sup> Corresponding Author: SungKyunKwan University Electric & Electronics Engineering Department, kleeg@skku.edu, 정회원

<sup>\*</sup> ETRI Optical Internet Research Department Optical Access Laboratory, soolee@etri.re.kr 논문번호: KICS2014-03-109, Received March 31, 2014; Revised June 20, 2014; Accepted June 20, 2014

다. 이를 위해 CMOS 포토닉스 기술 기반의 다중/역다중화기 (MUX/DeMUX)와 광검출기 어레이로 구성되는 단일 집적 PIC, CMOS 공정 기반의 어레이 TIA 및 어레이 드라이버로 구성되는 Electrical integration circuit (EIC), 그리고 VCSEL 어레이 광원을 단일 패키지화하여 OLT에 적용할 수 있는 멀티채널 송수신모듈 개발이 필요하다.

Transimpedance amplifier (TIA)는 광수신기에서 Photo diode (PD)에 의해 입사되는 광신호로부터 변환된 전류신호를 증폭하여 다음 블록에 전압신호로 전달하기 위해 적용된다. 최근에는 순수 CMOS TIA 를 기반으로 하는 많은 향상된 고성능 TIA 기술이 연구되고 있는데, 대표적으로 10 Gb/s 이상의 대역폭을 구현하기 위해 인덕터 피킹 기술이 요구되고 있으나단일 칩으로 제작 시 점유면적이 크고 비용이 커지는단점이 있고, 대역폭 또한 입력 노드의 큰 기생 PD 용량으로 인해 크게 제한된다<sup>11</sup>. 본 논문에서는 이를 극복하기 위해 넓은 대역폭을 갖는 고성능 TIA 를 제안한다.

이를 위해 II장에서 TIA 구조 및 회로설계에 대하여 기술하고, III장에서 레이아웃 및 시뮬레이션 결과를 기술한다. 그리고 IV장에서 칩 성능을 측정하기 위한 환경구성, 그리고 중요 기능 및 성능을 측정하고 그 결과를 분석하며, 끝으로 V장에 결론을 맺는다.

# Ⅱ. TIA 구조 및 회로 설계

# 2.1 요구규격

표 1에 최근 연구되고 있는 0.13  $\mu$ m CMOS 기반의 10-Gb/s TIA 연구 추세<sup>[2-4]</sup>를 바탕으로 경쟁력을 갖는 기능 및 성능을 가지면서 저가격, 저전력 및 소형의 0.13  $\mu$ m CMOS 기술 기반의 4×10 Gb/s TIA 요구 규격을 제시한다.

표 1. R4×10 Gb/s 어레이 TIA 요구사항 Table 1. Requirements for 4×10 Gb/s Array TIA

| Item                | Value           |  |  |

|---------------------|-----------------|--|--|

| Data rate           | 10 Gb/s         |  |  |

| Bandwidth           | 8 GHz           |  |  |

| Input noise current | < 100 pA/√Hz    |  |  |

| TZ gain             | <b>55</b> dBΩ   |  |  |

| Settling time       | 75 ns           |  |  |

| Sensitivity         | -27 dBm @10-12  |  |  |

| Current range       | 0~15 mA         |  |  |

| Resolution          | 0.1~0.3 mA/step |  |  |

| Supply voltage      | 1.2 V/3.3V      |  |  |

# 2.2 TOP 블록도

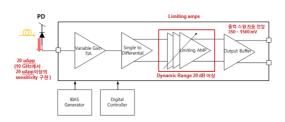

그림 1은 제안된 TIA TOP 블록도이다. PD의 전류를 입력으로 받아 1차적으로 TIA 코어에서 전압으로 출력한다. TIA 코어에서 출력된 전압은 싱글 출력이므로 차동 출력을 위해 Single to differential amplifier (SD)를 설계한다. Single to differential로 차동 출력된 전압은 최종 단에서 원하는 swing 만큼 출력되기 위해 Limiting amp를 통해 충분히 증폭된후, 출력버퍼를 거쳐 최종적으로 전압이 출력된다. 리미팅 증폭기 및 출력버퍼의 Tail current를 제어하여최종 출력 swing을 제어할 수 있다. 바이어스 전압은 BGR을 통해 일정한 전압이 내부에서 공급되며, 외부모드로 모두 공급할 수도 있다. PD의 입력이 20 μA이상 제공되어야 한다는 지침에 따라 최소 전류인 20 μA를 입력으로 하여 시뮬레이션을 진행하였다.

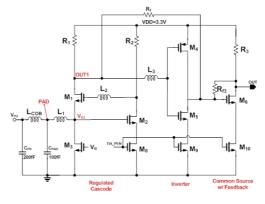

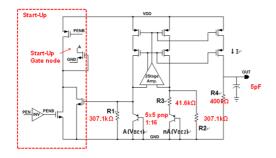

그림 2는 제안된 TIA 코어 회로이다. 대역폭 증가를 위해 다단 구성하였고, 최종 단에서 보이는 MOS의 커패시턴스를 줄이기 위해 인덕터를 직렬로 단 사이에 연결하였다. 또한 높은 주파수에서 원하는 수준의 이득을 가질 수 있도록 단은 Regulated Cascode, Inverter, CS Amplifier 등의 3단으로 구성하였다. 앞에 설명한 바와 같이 Regulated Cascode는 입력 임피

그림 1. TIA TOP 블록도. Fig. 1. TIA Top Block Diagram.

그림 2. TIA 코어 회로 Fig. 2. TIA Core Schematic.

던스는 작고, Transimpedance 이득은 크다는 장점을 가지고 있다<sup>15,6]</sup>. 인덕터의 경우 3개만 사용하여 면적 을 최소화하였고, 레이아웃 시 발생할 수 있는 기생용 량 또한 최소화 되도록 하였다.

TIA 경우, 입력이 PD의 전류이기 때문에, PD의 Cap, Pad Cap, 본당 와이어 인덕턴스를 고려하여 회로도를 구성하고 시뮬레이션을 진행하였다. 상용 PD(BPD2010-12\_Cosemi사)<sup>[7]</sup>의 커패시턴스 0.2 pF를 TIA 입력에 적용하였다. 상용 PD의 대역폭 특성으로부터, PD의 커패시턴스 성분에 의해 대역폭이 많은 부분 영향을 받게 된다는 사실을 알 수 있다.

#### 2.3 SD (Single to Differential Amplifier)

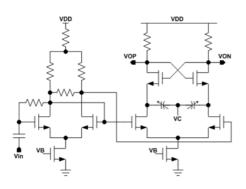

그림 3은 Single to differential (SD)회로이다. TIA 코어 출력이 차동이 아니기 때문에, 차동 출력 전압을 만들어주기 위한 회로이다. 차동 출력을 이용하는 이 유는 이를 통해 2차 고조파 (harmonic)에 대한 영향을 최소화할 수 있을 뿐만 아니라 공통 모드 잡음 (Common mode noise)를 제거할 수 있다는 장점을 갖기 때문이다. 이 구조는 차동 출력을 내보내 주면서 어느 정도의 등화 (equalizing) 기능도 갖도록 구성하 였다. Active inductor 구조를 이용하여 2 단으로 구성 되어 있어서 넓은 대역폭과 차동 균등 품질 (Differential balancing quality)를 보장한다. 첫 단에 서는 면적 때문에 인덕터를 사용하지 않고 저항 부하 를 사용하였다. 입력 신호는 Coupling capacitor를 통 해 AC 신호만 통과할 수 있고, 첫 단의 RC가 피드백 저항 및 셀프 바이어스 저항 기능을 한다. 첫 단의 출 력 사이에 있는 저항은 출력 차동 신호의 공통 모드가 동일하게 유지하는 역할과 차동 신호의 크기를 제어할 수 있도록 구성하였다. 두 번째 단에서는 주로 첫째 단 에서 발생하는 불일치 (mismatch)를 맞추는 기능, 대 역폭 향상 및 차동 밸런스 (Differential balancing)을

그림 3. Single to Differential 회로. Fig. 3. Single to Differential schematic.

향상시킨다<sup>[8]</sup>.

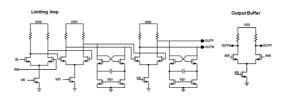

# 2.4 리미팅 증폭기 및 출력 버퍼

그림 4는 Limiting Amplifier와 Output Buffer의 회로도이다. TIA의 출력전압을 Limiting amplifier에서 증폭시킨 후, Output buffer를 통해 출력된다. Limiting amplifier도 대역폭 향상 향상에 이슈가 존재하기 때문에, Negative impedance converter (NIC)를 각 단 사이에 설계하여 종단에서 보이는 커패시턴 스를 최대한 감소시키고자 하였다. Negative capacitance 값을 만드는 식은 다음 식 (1)과 같다.

$$Z_{C} = -\frac{1}{SC_{c}} \frac{gm + s(C_{gs} + 2C_{c})}{gm - SC_{gs}}$$

(1)

Zc은 negative capacitance의 임피던스를 나타내며 Cc에 비례한다. Cc는 Cross coupled circuit 사이에 위치한 커페시턴스이다<sup>19</sup>.

그림 4에서 볼 수 있듯이 일반적인 증폭기와 같이 이득을 키우기 위해 MOSFET 부하를 사용할 경우 대역폭이 많이 줄어드는 문제가 발생한다. 따라서 부하로서 인덕터를 사용하면 넓은 대역폭 특성을 가질 수 있지만, 앞서 설명한 내용과 같이 면적 이슈가 존재하기 때문에 사용하기 어렵고 오히려 라인 길이에 의한 기생 커패시턴스에 의해 성능 향상이 크게 나타나지 않아 저항 부하를 사용하였다. 대역폭과 이득을 향상시키기 위해 다단 구성하였으며, 최종 출력의 스윙을 원하는 수준으로 제어하기 위해 Limiting amplifier와 Output buffer의 Tail current를 조절할 수 있도록 바이어스 부분에도 외부에서 조절할 수 있는 2 bits External control mode를 적용하였다.

그림 4. Limiting Amplifier & Output buffer 회로. Fig. 4. Limiting Amplifier & Output buffer schematic.

# 2.5 바이어스용 저전압 BGR

그림 5는 TIA 각 블록에 필요한 바이어스 전압의 경우 PVT (Process, Voltage, Temperature) 변화에 대해서 비교적 일정한 전압을 만들어 주어야 하기 때문에, Band gap reference (BGR) 회로가 필요하다.

그림 5. BGR 회로. Fig. 5. BGR Schematic.

하지만 일반적인 BGR 회로의 경우 계산에 의해 1.2V 의 출력이 나오기 때문에, 현재 TIA의 사용되는 전원인 1.2V로는 이를 만들어 낼 수 없다. 따라서 저전압 BGR 회로를 구성하여 0.4V 정도의 BGR 전압을 생성하여 이를 이용해 바이어스를 공급할 수 있도록 구성하였다. BGR에 들어간 BJT는 온도 센서로서의 역할을 하여 출력 전압이 온도에 덜 민감하도록 하는 역할을 하며, BGR 설계에 사용되는 증폭기는 두 개의 Differential input 전압이 같아지도록 Feedback loop가 형성되어 전압이 안정적으로 공급할 수 있는 역할을 한다. 증폭기의 이득이 높을수록, BGR의 PSRR과작은 온도 변화를 가진다. 저항들의 비율을 이용하여일정한 전압을 만들어 낸다. BGR의 출력 전압은 다음의 식 (2)로부터 구할 수 있다<sup>10</sup>.

$$V_{out} = IR_4 = m\left(\frac{V_{BE1}}{R_1} + \frac{V_T \ln n}{R_3}\right) R_4 \tag{2}$$

또한, 초기 동작시 문제가 없도록 Start Up 회로를 추가하여 초기 노드 전압 이슈가 없도록 설계하였다.

# Ⅲ. 레이이웃 및 시뮬레이션 결과

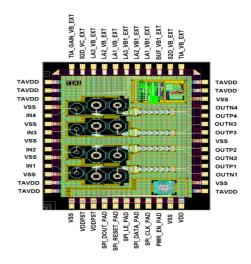

그림 6은 TIA 4채널의 탑 레이아웃을 보여준다. 각채널은 크게 TIA 4 채널과 Bias circuit 및 SPI로 구성되어 있으며, 최대한 채널간 mismatch가 없도록 구성하였다. 바이어스 블록에서 전압을 각 채널에 공급해 주며 SPI 인터페이스를 통해 제어된다.

최종 Top layout의 경우, 1.9 µm × 2.2 µm의 크기를 갖는다. 1 채널 레이아웃을 보면 TIA 코어, Single to differential, Limiting amplifier 1, 2, 3, Output buffer로 구성되어 있음을 알 수 있다. 1 채널 크기는 1235 µm × 290 µm 이다.

TIA 칩 형상을 보면 입력과 출력의 부하를 최소화

그림 6. 4채널 TIA 탑 레이아웃. Fig. 6. Top Layout for 4 channels TIA.

하기 위해, 좌측을 입력, 우측을 출력으로 하여 출력 마다 250 µm의 피치를 갖도록 배치하였다. 바이어스 전압을 외부에서도 인가할 수 있도록 외부 모드를 두 고 각 채널의 Bias pad를 배치하였다. TIA의 4 채널 입력은 모두 250 µm 피치 간격을 맞추어 외부 인터페 이스와도 용이하도록 배치하였다. 아래 부분에 컨트롤 러인 디지털 로직 SPI 를 배치하여 디지털과 아날로 그와의 전원을 분리하였다.

# 3.1 AC 시뮬레이션 결과

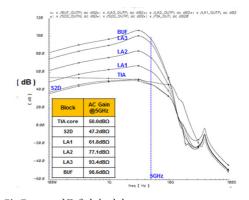

그림 7은 전체 TIA 에 대한 post simulation level 의 AC 시뮬레이션 결과를 보여준다. TIA 코어만으로는 대역폭을 유지하면서 이득을 향상시키기 어렵기 때문에, Limiting amplifier를 3단을 설계하여 최종 단까지 이득을 점차 증가시켰다. 그림 11. AC 시뮬레이션 결과에서 볼 수 있듯이, TIA 코어의 이득은 50 dB

그림 7. AC 시뮬레이션 결과. Fig. 7. AC Simulation Result.

$\Omega$ 이지만, LA1, LA2, LA3 회로를 거치면서 이득은 93.4 dB $\Omega$ , Output Buffer를 거친 최종 이득은 98.6 dB $\Omega$ 을 확보하다.

#### 3.2 Transient 시뮬레이션 결과

그림 8은 전체 TIA Transient 시뮬레이션 결과를 보여준다. 데이터 복원의 확인을 위해 기본 High/Low 가 반복되는 패턴과 랜덤한 데이터 패턴인 "10101100" 패턴을 넣어 각 단 마다 데이터 복원이되는지 여부를 시뮬레이션을 통해 확인하였다. 그림 8의 BUF\_VOUTP,N 에서 INPUT 데이터 패턴대로 전체 TIA 출력이 되는 것을 확인할 수 있다.

그림 8. TIA Transient 시뮬레이션 결과. (a) 랜덤 데이터 패턴, (b)01반복 패턴.

Fig. 8. TIATransient Simulation result. (a) Random data pattern, (b) (01 pattern).

#### 3.3 출력 스윙 결과

그림 9는 TIA의 출력 스윙 제어 시뮬레이션 결과 이다. 20 µA의 전류 입력을 인가했을 때 바이어스 전

그림 9. TIA 출력 스윙 제어 시뮬레이션 결과. Fig. 9. TIA Output Swing Control Simulation Result.

압 2 비트로 만들어 제어함으로써, 출력 스윙이 260 mV 부터 830 mV (Differential: 520 mV ~ 1660 mV)까지 변하는 것을 확인하였다.

# Ⅳ. 측정 및 결과분석

#### 4.1 측정환경 구성

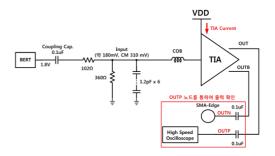

그림 10은 측정 환경 구성을 보여준다. 측정기기는 High Speed Oscilloscope (DSA 71254C Digital Serial Analyzer 12.5GHz), BERT (J-BERT N4903B 12.5Gb/s), Network Analyzer (E5071B 300 kHz - 8.5 GHz), DC Power Supply를 사용하여 측정하였다. 다이오드를 등가회로로 대체하기 위해 저항과 커패시터를 연결하였다. BERT를 통해 입력 1.8V가 인가된후 실제로는 감쇄되어 인가된다. OUTP 노드를 통하여고속 오실로스코프를 이용하여 측정하였다.

그림 11의 10 Gb/s 4 채널 TIA 성능 측정 보드는 Chip-on-board로 TIA 4 채널 입력을 한 모서리에 250 µm 피치 간격으로 배치하여 트랜시버 내 다음 단 스위치인 DMUX와 인터페이스가 용이하도록 제작하였다. 4 layer 기판으로 제작되었으며 Line의 Parasitic capacitance의 영향을 크게 받을 것을 고려하여 Top,

그림 10. 10 Gb/s TIA 측정환경 구성도. Fig. 10. Measuring Environment for 10 Gb/s TIA.

그림 11. 10 Gb/s 4채널 TIA 어레이 칩 성능 측정용 보드 Fig. 11. Performance Test Board for 10 Gb/s 4 channel TIA Array Chip.

Bottom 양면에 소자를 배치하여 Line 길이를 최소화 시키는 방향으로 제작하였다. Input과 Output의 Loading parasitic을 최대한 줄이기 위해 Input과 Output의 길이를 최대한 짧게 배치하였다.

# 4.2 측정결과

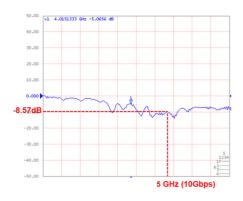

#### 4.2.1 반환 손실 (Return loss) S11

그림 12는 네트워크 어낼라이저를 통해 S11을 측 정한 결과로서 Input matching S<sub>11</sub>값은 -8.57 dB를 얻 는다.

그림 12. 네트워크 어낼라이저를 이용한 반환 손실 (Return loss) S11 측정결과.

Fig. 12. Return loss using Network Analyzer Measurement.

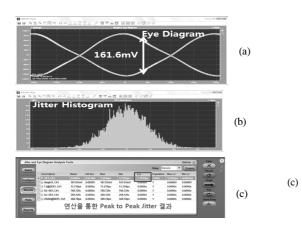

#### 4.2.2 아이 다이어그램 및 지터

그림 13은 주파수에 따른 출력 아이 다이어그램 및 지터 측정 결과를 보여준다. 입력 주파수는 2 GHz (4Gb/s), Jitter peak to peak 는 5 GHz에서 7.2ps로

그림 13. 주파수에 따른 출력 아이 다이어그램 및 지터. (a) Eye Diagram, (b) Jitter, (c) Calculation result of Jitter and Eye Diagram using Analysis tool.

Fig. 13. Output Eye Diagram and Jitter according to frequency.

측정되었다.

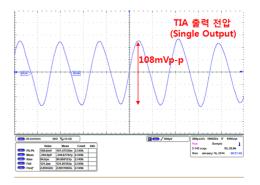

#### 4.2.3 이득

그림 14에 보인 바와 같이 출력 Vp-p는 108mVp-p (Differential Output = 216mVp-p)이고, 입력 전류는 입력 전압 스윙 및 시뮬레이션을 통해 54.4 uA 의 Ip-p값을 얻는다. 이를 통해 식 (3)과 같이 이득을 구하면 71.8 dBΩ을 얻는다.

$$\begin{split} TIA_{gain} &= 20\log\left(\frac{Output\ V_{pk-pk}}{Input_{I_{pk-pk}}}\right) \\ &= 20\log\frac{108^*2m}{54u} = 71.81\,dB\Omega \end{split} \tag{3}$$

그림 14. TIA 이득 측정 결과. FIG. 14. TIA Gain Measurement.

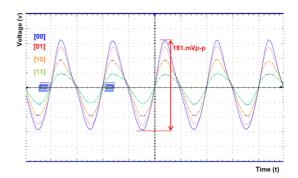

## 4.2.4 다이내믹 레인지

그림 15는 TIA SPI 제어에 따른 출력 다이내믹 레 인지 변화를 보여준다. Real input 30 mv에서 Single output 63.66 m $V_{P-P}$ ~191m $V_{P-P}$ (Diff.127.32 m $V_{P-P}$ ~382 m $V_{P-P}$ )로 측정되었다.

그림 15. 다이내믹 레인지 측정 결과. Fig. 15. Dynamic Range Measurement.

#### 4.2.5 Sensitivity

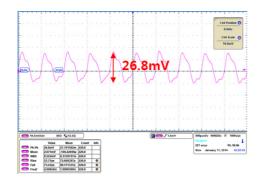

그림 16은 Sensitivity 측정결과를 나타낸다. 현재 측정 장비로는 전류 측정이 어려워 BERT 입력과 Oscilloscope 를 통한 입력파형을 토대로 4 Gb/s 입력 레벨에서 시뮬레이션을 통하여 전류를 도출하고 계산을 통하여 Sensitivity 를 구하였다. TIA 입력 26.8 mV (BERT에서 500 mV 입력 시) Output이 정상 출력되는 BERT의 최소 입력은 85 mV이다. 이 때 비율적으로 고려하면 TIA 입력은 4.556 mV이다. 시뮬레이션을 통하여 현재 측정 상황을 모델링한 후, 입력전류에 대한 특성 확인한 다음 Sensitivity를 도출하였다. 현재 입력 전압을 토대로 시뮬레이션 진행해 본결과 입력 전류는 53.448  $\mu$ App이다. 이 때 계산된 Sensitivity는 -33.62 dBm (입력 임피던스 = 152  $\Omega$ ,  $\Delta$   $P = \Delta I^2 \times R$ 로 계산)로서 규격대비 양호한 결과를 얻었다.

그림 16. Sensitivity 측정결과. Fig. 16. Sensitivity Measurement.

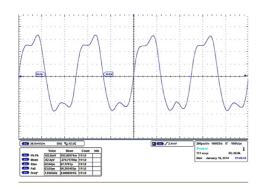

#### 4.2.6 Rising & Falling Time

그림 17은 4 Gb/s 에서 Rising time과 Falling time 측정결과를 보여주며 각각 62 ps와 63 ps 로 측정되

그림 17. Rising/Falling Time 측정결과. Fig. 17. Rising/Falling Time Measurement.

었다.

#### 4.3 결과분석

최종 출력 최대 이득은 98.6 dB 오이고 크기는 10 k 요으로 이득이 타 상용 소자보다 우수하며, 또한 전력 소모 면에서도 1 채널 당 47.64 mW로 상당히 적은 것을 알 수 있다. 4 채널임에도 불구하고, 4 채널 어레이 칩의 면적은 1.9 mm × 2.2 mm로서 상용 칩 대비작게 제작되었다.

설계된 TIA는 Single to differential amplifier 회로가 어느 정도 equalizing 기능을 하고 있기 때문에 발생하는 DC offset을 줄여줌으로써 DC offset이 거의 발생하지 않는 것을 시뮬레이션을 통해 확인을 하였으며 따로 Offset cancellation 기능이 추가되어 있지 않다. 이득이 최대 98.6 dB요으로 매우 높기 때문에, 조금 더 확실히 DC offset 발생을 최소화시키기 위해 Offset cancellation 기법을 추가하고, 현재 설계된 TIA가 온도가 변화할 때, ADC를 이용하여 자동적으로 온도를 보상하여 정상동작 할 수 있도록 Automatic temperature calibration 기능을 추가할 필요가 있다.

표 2. 타사 상용 TIA 제품과 제안된 TIA 칩간 성능규격 비교

Table 2. Comparison of Performance Specification between Commercial and proposed 10Gb/s TIA.

|                              | Model (Company)                        |                                             |                      |                               |                    |

|------------------------------|----------------------------------------|---------------------------------------------|----------------------|-------------------------------|--------------------|

| Parameter                    | ONET854<br>1T<br>(Texas<br>Instrument) | PSRX100-<br>1<br>(PHOTON<br>IC<br>SOLUTION) | VSC7978<br>(VITESSE) | ADN2820<br>(Analog<br>Device) | 본<br>연구결과          |

| Data Rate<br>(Gb/s)          | 11.3                                   | 10                                          | 9.9-11.3             | 10.7                          | 10                 |

| Gain                         | <b>4 k</b> Ω                           | <b>4 k</b> Ω                                | <b>4 k</b> Ω         | 5 kΩ                          | 71.81<br>dBΩ       |

| Bandwidth<br>(GHz)           | 9                                      | 8                                           | 8                    | 9                             | 7                  |

| Sensitivity<br>(dBm)         | -20                                    | -27                                         | N.A.                 | -19.3                         | -33.62             |

| Supply<br>Voltage (V)        | 3.3                                    | 3.3                                         | 3.3                  | 3.3                           | 1.2                |

| Power<br>Consumption<br>(mW) | 90                                     | 181.5                                       | 140                  | 200                           | 31                 |

| Area<br>(Package or<br>Die)  | 870 μm×<br>1036 μm                     | 5.6 mm×<br>16.2 mm                          | N.A.                 | 870 μm×<br>1060 μm            | 1.9 mm ×<br>2.2 mm |

## V. 결 론

본 논문에서는 0.13 µm CMOS 공정으로 4×10 Gb/s TIA 어레이 칩을 구현하였다. TWDM-PON의 광트랜시버에 적용되는 TIA를 위해 상용화 칩 보다 효율적으로 넓은 대역폭을 가지면서 적은 소모 전력과 작은 크기의 칩을 저 가격으로 구현 할 수 있음을 입증하였다. 구현된 칩은 적은 면적과 적은 소모전력 및 62 ps와 63 ps의 Rising/Falling time 을 각각 제공한다. 본 연구에서 구현된  $0.13\mu m$  CMOS 공정의 10 Gb/s 4채널 TIA 어레이 칩은 Real input 30 mV에서 Single output  $63.66 mV_{pp} \sim 191 mV_{pp}$ 의 다이내믹레인지를 제공하고, -33.62 dBm 의 sensitivity를 제공할 수 있다. 1.2V 공급 전압에서 소모 전력은 31 mV/channel 이고, 칩 크기는  $1.9 mm \times 2.2 mm$  이다. 따라서 본 칩은 TWDM-PON시스템내 Optical transceiver에 적용시 Network flexibility, scalability 및 upgradeability를 제공할 수 있다.

# References

- [1] T.-H. Nöll, T.-W. Lee, and H.-H. Park, "Design of transimpedance amplifier for optical receivers in 0.13 µm CMOS," *Int. Conf. Optical Internet (COIN)*, pp. 1-3, Jeju, Korea, Jul. 2010.

- [2] X. Yin, et al., "A 10Gb/s burst-mode TIA with on-chip reset/lock CM signaling detection and limiting amplifier with a 75ns Settling Time," *IEEE Int. ISSCC*, pp. 416-418, San Francisco, CA, Feb. 2012.

- [3] T. D. Ridder, et al., "A 2.7V 9.8Gb/s burst-mode TIA with fast automatic gain locking and coarse threshold extraction," *IEEE Int. ISSCC*, pp. 220-221, San Francisco, CA, Feb. 2008.

- [4] D.-U. Li and H.-C. Chen, "10Gb/s 0.13µm CMOS laser drivers with extinction ratio control using thermistors," *Solid State Circuits Conf. (ESSCIRC 2007)*, pp. 260-263, Munich, Sept. 2007.

- [5] E. Hammoudi, B. Imad, and D. Mohamed, "High bandwidth 0.35µm CMOS transimpedance amplifier," *Int. Conf. Complex Systems (ICCS), Digital Object Identifier*, pp. 1-6, 2012.

- [6] T. Takemoto, H. Yamashita, T. Yazaki, N. Chujo, Y. Lee, and Y. Matsuoka, "A 4x

- 25-to-28Gb/s 4.9mW/Gb/s —9.7dBm high-sensitivity optical receiver based on 65nm CMOS for board-to-board interconnects," *IEEE Int. ISSCC*, pp. 118-119, San Francisco, CA, Feb. 2013.

- [7] Company: Commercial PD (BPD2010-12\_Cosemi).

- [8] Y. Chen, et al., "0.0012, 8mW, single-to-differential converter with < 1.1% data cross error and < 3.4 ps RMS jitter up to 14 Gbit/s data rate," *IET ELECTRONICS Lett.*, vol. 49, no. 11, pp. 692-694, May 2013.

- [9] X. Zhang, et al., "Design of lower power 4x10Gb/s VCSEL driver array," IEEE MTT-S Int. Microwave Workshop Series on Millimeter Wave Wirel. Technol. Appl. (IMWS), pp. 1-3, Sept. 2012.

- [10] Y.-T. Lin, et al., "A Low-Variation, Low-Voltage CMOS Bandgap Reference Circuit," Dept. of Electronic Eng., Lunghwa Univ. of Science and Technol., Issue 25, Jun. 2008.

#### 양 충 열 (Choong-reol Yang)

1983년 : 건국대학교 전자공학 과 공학사

1998년 : 충남대학교 전자공학과 공학석사

2007년 : 충남대학교 전자공학과 공학박사

1992년 6월~현재: 한국전자통

신연구원 광인터넷연구부 광가입자연구실 책임연 구워

<관심 분야> 광통신, 광패킷스위칭, 광인터넷, 아 날로그 집적회로 설계

# 이 강 윤 (Kang-yoon Lee)

1996년 : 서울대학교 전기공학 공학사

1998년 : 서울대학교 전기공학 과 공학석사

2003년 : 서울대학교 전자공학과 공학박사

2005~2011년 : 건국대학교 전 기전자공학과

2012~2014년: 성균관대학교 전자전기공학과 부교수 <관심 분야> CMOS RF Transceiver, 아날로그 IC, 아날로그-디지털 혼성모드 피냐 시스템 설계

# 이 상 수 (Sang-soo Lee)

1988년 : 인하대학교 전자공학과 공학사

1990년 : 인하대학교 전자공학과 공학석사

2001년 : 인하대학교 전자공학과 공학박사

1990년 7월 3일~2013년 1월:한

국전자통신연구원 현재: 광인터넷연구부 광가입자연구실 실장 <관심 분야> 광액세스망, WDM-PON, 에너지 효율 망기술, 아날로그 집적화