# 논문 14-39A-09-11

# 버틀러 매트릭스의 설계 및 구현

# 강상기\*

# Design and Implementation of **Butler Matrix**

Sanggee Kang\*

#### 약 요

주파수 이용효율을 높이는 방법으로 범포밍 기술을 사용한다. 본 논문에서는 무선랜 주파수 대역에서 RF 빔포머로 사용할 수 있는 버틀러 매트릭스를 설계 및 제작하였다. 구현한 버틀러 매트릭스는 2.4 2.485GHz의 주파수 범위에서 삽입손실은 최대 6.7dB, 최대 위상천이 오차는 -6.51°~7.17° 갖는다.

**Key Words:** Butler Matrix, Beam forming, Wi-Fi, MIMO

### **ABSTRACT**

Beam forming techniques are used to increase the efficiency of using frequency. In this paper we design and implement Butler matrix to be used for ISM band. The implemented Butler matrix has the insertion loss of maximum 6.7dB and the maximum phase shift error of  $-6.51^{\circ}$  ~  $7.17^{\circ}$  over 2.4 ~ 2.485GHz.

### I. 서 론

주파수 이용 효율을 높이기 위해서 다양한 연구개 발이 진행되고 있고, 그 중의 하나가 빔포밍 기술을 사용하는 것이다[1] 범포밍 방법에는 기계적인 방법 과 전기적인 방법이 있으며, 전기적인 방법에는 위상 편이와 주파수편이를 이용하는 방법이 있다[1]. 위상 편이를 이용한 빔포머에서는 신호를 병렬로 인가해 야 한다. 본 논문은 위상편이를 이용한 범포밍 방법 중에 하나인 버틀러 매트릭스의 설계 및 제작에 대해 서 기술한다.

## Ⅱ. 본 론

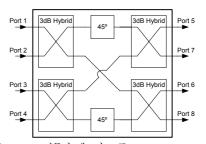

버틀러 매트릭스의 구조는 그림 1과 같다. 그림 1 과 같이 버틀러 매트릭스의 단자 1, 2, 3, 4를 입력단 자, 단자 5, 6, 7, 8을 출력단자라 하고, 버틀러 매트릭 스가 이상적인 성능을 갖는다고 하면, 입출력 신호 사 이에는 표 1과 같은 관계가 성립한다<sup>[2,3]</sup>. 표 1에 기술 된 입출력 신호의 관계는 버틀러 매트릭스를 빔포밍 수단으로 사용할 수 있음을 보여준다.

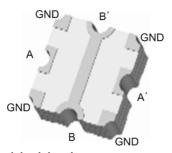

마이크로스트립 선로로 버틀러 매트릭스를 구현할 경우 구현상의 어려운 점은 신호선의 교차가 반드시 필요하다는 점이다. 그림 1의 버틀러 매트릭스의 구조 에서도 아래쪽 45° 지연선로의 바로 위에서 신호선이 교차함을 볼 수 있다(물리적으로 연결된 port 1 - port 8 사이의 신호선과 port 4 - port 5의 신호선이 교차 함). 본 논문에서는 교차형소자(cross over device)를 사용함으로써 신호선의 교차 문제를 해결하였다. 교차 형소자의 모양은 그림 2와 같다. 그림 2에서 알 수 있 듯이 교차형소자는 교차하는 신호선을 물리적으로 격 리하는 구조로 되어있다.

설계한 버틀러 메트릭스의 성능을 확인하기 위해서

그림 1. 4 x 4 버틀러 매트릭스 구조 Fig. 1. Configuration of 4 x 4 Butler matrix

표 1.4 × 4 버틀러 매트릭스의 입출력 특성 Table 1. Input/output characteristics of 4 x 4 Butler matrix

| 1 de la |                                                                            |  |

|---------------------------------------------|----------------------------------------------------------------------------|--|

| Input                                       | Output(Port 5, 6, 7, 8)                                                    |  |

| ron i                                       | equal amplitude of Pin/4 and -45° of phase shift at each port              |  |

| Port 2                                      | qual amplitude of Pin/4 and 135° of phase shift at each port               |  |

| Port 3                                      | equal amplitude of Pin/4 and -135° of phase shift at each port             |  |

|                                             | equal amplitude of $P_{in}/4$ and $45^{\circ}$ of phase shift at each port |  |

First Author: Kunsan National University, Dept. of Information & Telecommunication Engineering, skkang@kunsan.ac.kr, 정회원 논문번호: KICS2014-08-296, Received December 22, 2014; Revised December 22, 2014; Accepted December 22, 2014

그림 2. 교차형소자의 모양 Fig. 2. Shape of the cross over device

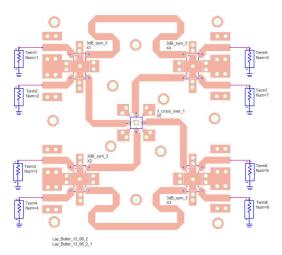

시뮬레이션을 하였으며, 시뮬레이션의 정확도를 높이기 위해서 EM(electromagnetic) 시뮬레이션을 수행한후에 소자(3dB 하이브리드와 교차형소자)들을 추가해서 시뮬레이션하는 방법을 사용하였다. 그림 3은 EM 시뮬레이션 결과에 3dB 하이브리드와 교차형소자를 추가해서 시뮬레이션하기 위한 회로 구성도이다.

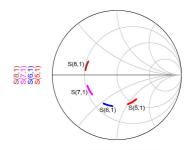

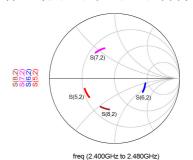

설계한 버틀러 매트릭스의 시뮬레이션 결과는 그림 4와 같다. 통상적으로 버틀러 매트릭스의 시뮬레이션 결과는 주파수별 위상과 크기를 비교해서 나타내었으나, 스미스 도표에 시뮬레이션 결과를 나타내면 버틀러 매트릭스의 성능을 직관적으로 알 수 있다. 그림 4의 (a)는 단자 1에 인가된 신호가 단자 5, 6, 7, 8로 크기는 동일하고 위상이 -45°씩 천이된 신호가 출력됨을 보여준다. 그림 4의 (b)는 단자 2에 인가된 신호가 단자 5, 6, 7, 8로 크기는 동일하고 위상이 135°씩 천이한 신호가 출력됨을 보여준다. 단자 3과 단자 4에 인가된 신호에 대한 시뮬레이션 결과도 그림 4와 유

그림 3. EM과 회로 소자의 시뮬레이션을 동시에 수행하기 위한 회로의 구성

Fig. 3. Circuit configuration of simultaneously EM and schematic circuit simulation

freq (2.400GHz to 2.480GHz)

(a) -45°(입력:단자 1, 출력: 단자 5,6,7,8)

(b) 135°(입력:단자 2, 출력: 단자 5,6,7,8)

그림 4. 설계한 버틀러 매트릭스의 시뮬레이션 결과 Fig. 4. Simulation results of the designed Butler matrix (Frequency range: 2.4 ~ 2.485GHz)

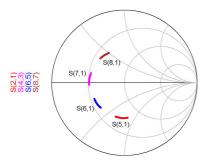

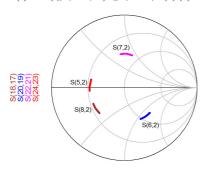

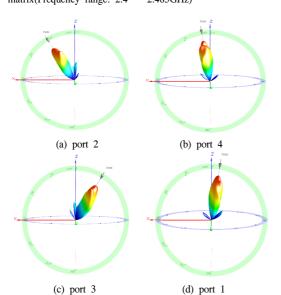

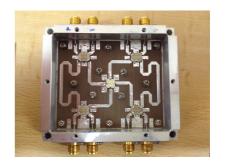

사하고 위상의 변화량만 다르므로 논문에서 기술은 생략한다. 그림 5는 구현한 버틀러 매트릭스의 성능을 측정한 결과이다. 그림 5와 그림 4을 비교해 보면 위상이 40° 정도 오프셋(RF 컨넥터 등에 의한 위상 오프셋)이 있을 뿐 그림 4의 시뮬레이션 결과와 아주 유사함을 알 수 있다. 제작한 버틀러 매트릭스의 성능측정 결과를 표 2에 요약해서 기술하였다. 그림 6은 제작한 버틀러 매트릭스를 마이크로스트립 어레이 안테나(4소자)의 급전부에 적용해서 범포밍 성능을 측정한 결과이며, 그림 6의 측정결과는 설계 제작한 버틀러 매트릭스가 범포머로 잘 동작함을 보여준다. 그림 7은 제작한 버틀러 매트릭스의 사진이다.

표 2. 제작한 버틀러 매트릭스의 성능 측정 결과 Table 2. Measurement results of the implemented Butler matrix

| Measurement Results          | Error                                                                                                                      |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 2.4 ~ 2.485GHz               | _                                                                                                                          |

|                              |                                                                                                                            |

| 6.25 ~ 6.7dB                 |                                                                                                                            |

|                              |                                                                                                                            |

| -44.35° ~-48.03°(@2.45GHz)   | -3.03°~0.65°                                                                                                               |

| 133.36°~135.45°(@2.45GHz)    | -0.45°~1.64°                                                                                                               |

| -130.36° ~-139.84°(@2.45GHz) | -4.84°~4.64°                                                                                                               |

| 38.49°~52.17°(@2.45GHz)      | -6.51°~7.17°                                                                                                               |

|                              | 2.4 ~ 2.485GHz<br>6.25 ~ 6.7dB<br>-44.35° ~-48.03°(@2.45GHz)<br>133.36° ~135.45°(@2.45GHz)<br>-130.36° ~-139.84°(@2.45GHz) |

freq (2.400GHz to 2.480GHz) (a) -45°(입력:단자 1, 출력: 단자 5,6,7,8)

freq (2.400GHz to 2.480GHz) (b)  $135^{\circ}($ 입력:단자 2, 출력: 단자 5,6,7,8) 그림 5. 제작한 버틀러 매트릭스의 성능 측정 결과 Fig. 5. Measurement results of the implemented Butler matrix(Frequency range:  $2.4 \sim 2.485GHz$ )

그림 6. 빔포머 성능 측정 결과 Fig. 6. Measured beamforming performance

그림 7. 제작한 버틀러 매트릭스 사진 Fig. 7. Photograph of the implemented Butler matrix

### Ⅲ. 결 론

2.4 - 2.485GHz에서 동작하며, 삽입손실 6.7dB인 4x4 버틀럭 매트릭스를 설계 및 제작하였다. 제작한 버틀러 매트릭스를 이용해서 실제 범포밍 성능을 측정한 결과는 본 논문의 버틀러 매트릭스가 범포머로 사용할 수 있음을 보여준다. 본 논문의 버틀러 매트릭스를 이용하면 주파수 이용효율을 높일 수 있다.

#### References

- [1] J. Litva and T. K.-Y. Lo, *Digital Beamforming in Wireless Communications*, Artech House, 1996.

- [2] J. Butler, "Digital, matrix and intermediate frequency scanning," *IEEE Trans. Antennas* and Propagation, vol. 3, pp. 66-70, Aug. 1965.

- [3] S. Kahng, K. Jang, J. Jeon, and D. Eom, "A miniaturized multi-function artificial-material butler matrix for antenna beamforming/ radars," in *Proc. KICS*, pp. 259-260, Jan. 2014.