# 사인-선형 위상차 방식의 차동 양자화된 직접 디지털 주파수 합성기

김 종 일<sup>\*</sup>, 이 현 승<sup>\*</sup>, 홍 찬 기<sup>°</sup>

The Differential Quantized Direct Digital Frequency Synthesizer Based on Sine-Linear Phase Difference

> Chong-il Kim\*, Hyun-seung Lee\*, Chan-ki Hong\*

> > 요 약

본 논문에서는 sine-linear phase difference 방식과 DPCM 방식의 차동 양자화 기술을 응용하여 새로운 ROM 압축방식을 제안하고 이를 이용하여 저전력 직접 디지털 주파수 합성기를 FPGA를 사용하여 설계 및 제작한다. ROM 크기를 줄이기 위해 사인파의 1/4 주기를 2<sup>N</sup>간격으로 표본화하여 양자화된 값을 양자화 ROM1에 저장하고 각 표본화 사이를 2<sup>K</sup>간격으로 표본화하고 ROM1에 저장된 표본화 값의 차이를 ROM2에 저장하여 ROM의 크기를 줄이는 방식을 사용한다. 이를 사용함으로써 기존 방식 대비 약 37%의 ROM 크기만 필요하게 되여 전력 소모를 줄일 수 있다.

Key Words: Direct Digital Frequency

Synthesizer, DDFS, sine-linear

phase difference, phase-to-sine

converter, ROM reduction

### **ABSTRACT**

In this paper, a new method to reduce the size of ROM in the direct digital frequency synthesizer (DDFS) is proposed. This method use the sine-linear phase difference method and differential PCM. The

new ROM compression method can reduce the ROM size by using the two ROM. The quantized value of sine-linear phase difference is saved by the ROM1 of the  $2^N$  sample period. The ROM2 save the difference between the original sine-linear phase difference value and the saved sample value of the ROM1. The ROM compression ratio of 37% is achieved by this method. Also, the power consumption is decreased according to the ROM size reduction.

## I. 서 론

주파수 합성기는 기준 주파수를 기본으로 여러 개의 주파수를 합성하여 발생시키는 소자이다. 주파수 합성기는 기존의 PLL방식을 이용한 간접 주파수 합성기와 디지털 소자를 이용한 직접 디지털 주파수 합성기(DDFS, Direct Digital Frequency Synthesizer) 방식이 있다<sup>[1]</sup>.

기존의 PLL을 이용한 간접 주파수 합성기는 정밀하고 세밀한 주파수 조정이 어렵고 주파수 변환 속도도 느리다. 직접 디지털 주파수 합성기는 주파수 발생 및 처리 속도가 매우 빠르며 광범위한 주파수 발생 범위를 가지고 있으나 여러 개의 디지털 소자와 많은 메모리 소자가 필요하게 되어 전력 소모가 크고 속도 저하의 원인이 된다. 따라서 주파수의 출력 품질을 보장하면서 속도가 저하되지 않도록 ROM의 크기를 줄이고자 하는 연구가 많이 수행되어지고 있다!<sup>2-5]</sup>.

이에 본 논문에서도 직접 디지털 주파수 합성기에서 사용되어지는 ROM의 크기를 감소시키는 방법을 제안하고 이를 이용하여 전력 소비가 낮고 원하는 주파수 품질을 얻을 수 있도록 한다.

# II. Sine-linear phase difference 방식의 차동 양자화 직접 디지털 주파수 합성기

ROM 테이블 방식은 출력에 필요한 정현파의 모든 샘플을 ROM에 저장하고 있어야 하기 때문에 출력 파형의 정확도에 비례하여 ROM 테이블의 크기가 커지게 된다. ROM 테이블 크기가 커질 경우 높은 전력과 ROM 테이블을 참조하는 속도가 매우 느려지게 되는

<sup>•</sup> First Author: Catholic Kwandong University, Department of Electronic Engineering, cikim@cku.ac.kr, 정회원

<sup>°</sup> Corresponding Author: Catholic Kwandong University, Department of computer science, chankih@cku.ac.kr, 정회원

<sup>\*</sup> Department of Electronic Engineering Catholic Kwandong University, 정회원 논문번호: KICS2016-09-263, Received September 20, 2016; Revised September 22, 2016; Accepted September 22, 2016

데, 이를 해결하기 위한 여러 가지 연구가 진행되어 오고 있고 그 중에 하나가 sine-linear phase difference 방식이다 $^{13}$ .

사인파의 위상( $\theta$ )이 0도부터 90도까지 변할 때, 그에 해당하는 사인 값을 ROM에 저장하는 대신 다음식의 값을 ROM에 저장한다.

$$f(\theta) = \sin(\theta) - \frac{2}{\pi} \cdot \theta \tag{1}$$

이렇게 함으로써 데이터 비트 수를 줄 일 수 있게 되다<sup>131</sup>.

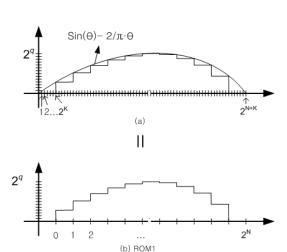

본 논문에서 제안하는 ROM 테이블 축소 기법은 이러한 sine-linear phase difference 방식과 양자화 방법 중 DPCM을 응용하여 ROM의 용량을 줄이고자한다. 즉, 그림 1처럼 두 개의 ROM을 이용하여 ROM1 에는 정현파의 샘플값을 저장하고 또 다른 ROM2에는 ROM1에 저장된 샘플 사이를 더 빠른 속도로 샘플하여 DPCM방식으로 저장한다.

원래 DDFS는 그림 1의 (a)처럼 사인파의 1/4 주기 중 4(1)의 값을  $2^{N+K}$ 간격으로 나누어 샘플하고 양자화 레벨을  $2^q$ 간격으로 나누어 q비트로 양자화 하여

그림 1. sine-linear phase difference와 ROM 축소 기법을 적용한 사인파의 양자화

Fig. 1. Quantization of sine using ROM reduction method and sine-linear phase difference

샘플 값을 저장한다. 그러나 이것을 먼저 그림 1의 (b) 처럼 먼저 사인파의 1/4주기를  $2^N$ 간격으로 나누어 샘 플하고 양자화 레벨을 2<sup>9</sup>간격으로 나누어 a비트로 양 자화하여 샘플 값을 ROM1에 저장한다. 두 번째로 사 인파와 ROM1에 저장된 (b)파형과의 차이를 구하여 그림 1의 (c)와 같은 파형을 구한 다음  $2^{N+K}$ 간격으로 나누어 샘플하고 양자화 레벨을  $2^p$ 간격으로 나누어 p비트로 양자화하여 샘플 값을 저장한다. 여기서  $p \ll q$ 가 된다. 이렇게 함으로써 ROM2에 저장되는 양자화 값의 최대 크기가 원래 데이터를 양자화하기 위한 최 대 크기보다 작기 때문에 ROM에 저장되는 데이터양 을 줄일 수 있게 된다. 전통적인 방법으로 정현파를 ROM에 저장시킬 때 ROM의 크기는  $2^{N+K} \times q$ 이다. 그러나 본 논문에서 제안한 ROM축소 방법으로 정현 파를 저장했을 때 ROM1에는  $2^N \times q$ , ROM2에는  $2^{N+K} \times n$ 가되어 감소되는 ROM의 크기는

$$2^{N+K} \times q - (2^N \times q + 2^{N+K} \times p)$$

(단  $p \ll q$ ) (2)

가 된다. 여기서 ROM2의 데이터 길이 p비트는 그림 1의 (c) 를 양자화 할 수 있을 정도로 충분히 길어야한다. 만일 그림 1의 (a)처럼 데이터 비트 길이가 q이 므로 양자화 간격  $\Delta v$ 는

$$\Delta v = \frac{1}{2^q} \tag{3}$$

이 되며 또한 어드레스 비트 길이가 N+K 이라 할 때 표본화 주기 T.은

$$T_s = \frac{1}{2^{N+K}} \tag{4}$$

이 된다. 똑같은 표본화 주기와 양자화 간격을 그림 1 의 (c)에 적용하면 임의의 위상 어드레스  $\theta$  인 경우 양자화 값  $\Delta(\theta)$ 은

$$\Delta(\theta) = \sin\left(\frac{\pi}{2} \times \frac{\theta}{2^{N+K}}\right) - \frac{2}{\pi} \left(\frac{\pi}{2} \times \frac{\theta}{2^{N+K}}\right)$$

$$\theta = 1, \dots, 2^{N+K}$$

(5)

이다. 따라서 ROM2에 저장되는 양자화 값의 최대값은

1180

$$\Delta m = \max \left[ \frac{\Delta(\theta) - \Delta(\theta - 1)}{\Delta v} \right]$$

(6)

따라서 ROM2에 이러한 양자화 값을 저장시키기 위해 필요한 비트수는

$$p = \lfloor \log_2 \Delta m + 1 \rfloor \tag{7}$$

이 된다.

이렇게 2개의 ROM에 저장된 데이터는 최종적으 로 ROM1의 데이터와 ROM2의 데이터를 더해서 최 종적인 사인파를 생성하게 된다. 예를들어 전통적인 ROM하나만을 사용했을 때 10비트의 어드레스 길이 와 8비트의 데이터 길이를 가지는 사인파와 sine-linear phase difference방식에 제안한 ROM 테이 블 축소 기법을 사용하여 얻어지는 ROM 축소 비율은 표 1처럼 요약할 수 있다. 전통적인 sine-linear phase difference를 이용한 ROM 테이블 기법으로  $2^{10} \times 8$ 의 ROM 용량 즉, 8,192비트의 용량이 필요하다. 여 기에서 제안한 알고리듬을 적용하면  $2^8 \times 8$ 의 ROM1 과  $2^{10} \times 1$ 의 ROM2을 사용했을 때 필요한 비트는 3,072비트로 기존 방식 대비 약 37%의 ROM 크기만 필요하게 된다. 또한 표에서 보는 바와 같이  $2^7 \times 8$ 의 ROM1과  $2^{10} \times 2$ 의 ROM2을 사용했을 때도 기존 방 식 대비 약 37%의 ROM 크기만 필요하게 된다.

## Ⅲ. DDFS의 FPGA 설계 및 실험

본 논문에서는 직접 디지털 주파수 합성기를 구현하기 위해 앞 절에서 제안한 ROM 테이블 축소 기법

표 1. Sine-linear phase difference방식과 2-ROM 사용 시축소된 ROM 크기의 비율

Table 1. Ratio of reduced ROM size of sine-linear phase difference and 2-ROM

|           |      | Address<br>bit<br>length | Data<br>bit<br>length | Data bit<br>number | Total<br>Data bit<br>number | ROM<br>capac<br>ity<br>rate<br>(%) |

|-----------|------|--------------------------|-----------------------|--------------------|-----------------------------|------------------------------------|

| 1- ROM    |      | 10                       | 8                     | 8,192              | 8,192                       | 100                                |

| 2-<br>ROM | ROM1 | 9                        | 8                     | 4,096              | 5,120                       | 62                                 |

|           | ROM2 | 10                       | 1                     | 1,024              |                             |                                    |

|           | ROM1 | 8                        | 8                     | 2,048              | 3,072                       | 37                                 |

|           | ROM2 | 10                       | 1                     | 1,024              |                             |                                    |

|           | ROM1 | 7                        | 8                     | 1,024              | 3,072                       | 37                                 |

|           | ROM2 | 10                       | 2                     | 2,048              |                             |                                    |

|           | ROM1 | 6                        | 8                     | 512                | 3,584                       | 44                                 |

|           | ROM2 | 10                       | 3                     | 3,072              |                             |                                    |

|           | ROM1 | 5                        | 8                     | 256                | 3,328                       | 40                                 |

|           | ROM2 | 10                       | 3                     | 3,072              |                             |                                    |

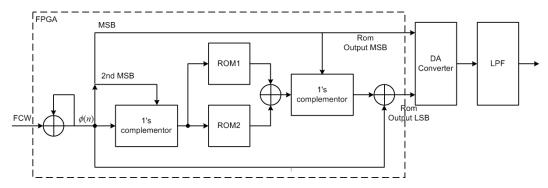

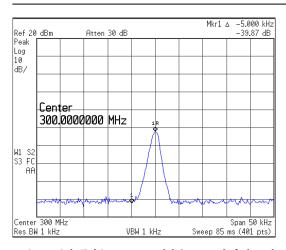

을 이용한 위상-사인 변환기를 FPGA를 이용하여 설계 및 제작하여 전체적인 DDFS를 제작하고자 한다. 직접 디지털 주파수 합성기는 앞에서 설명한 FPGA로 구현한 위상-사인 변환기와 이들의 출력을 아날로그로 변환하는 DA 변환기로 구성되어 진다. 앞 절에서 제안한 ROM 축소 기법을 이용한 위상-사인 변환기의 FPGA 블록도는 그림 2와 같다. 여기서 FCW는 최대 300MHz, 1Hz의 해상도를 얻기 위해 30비트의 FCW가 사용되어진다. 이렇게 제작된 DDFS의 시스템을 이용하여 출력 주파수가 300MHz의 출력 스펙트럼이그림 3에 나와 있다. 따라서 앞에서 제안한 2개의 ROM을 이용한 sine-linear phase difference 방식을

그림 2. Sine-linear phase difference 방식의 2-ROM 테이블 축소 기법을 이용한 위상-사인 변환기의 FPGA의 블록도

Fig. 2. FPGA block diagram of 2-ROM reduction method of sine-linear phase difference

그림 3. 중심 주파수 300MHz, 대역폭 50kHz의 출력 스펙 트럼 Fig. 3. Spectrum of the center frequency 300MHz and bandwidth 50kHz

이용하여 광대역의 주파수 합성기를 설계 및 제작 할수 있다.

## Ⅳ. 결 론

본 논문에서는 낮은 소비 전력과 높은 주파수를 얻고 ROM 크기를 줄이기 위해 sine-linear phase difference 방식과 DPCM 방식의 차동 양자화 기술을 응용하여 새로운 ROM 압축방식을 제안하고 이를 이용하여 저 전력 직접 디지털 주파수 합성기를 FPGA를 사용하여 설계 및 제작하였다. 새롭게 제안된 ROM 테이블 압축방식은 ROM 크기를 줄이기 위해 사인파를 양자화 할 때 차동 양자화 기술을 응용, 변형하여 두 개의 ROM을 사용한 압축방식을 이용한다. 표본화된 사인파의 양자화 값은 ROM1에 정현파의 샘플값을 저장하고 또 다른 ROM2에는 ROM1에 저장된 샘플 사이를 더 빠른 속도로 샘플 하여 DPCM방식으로 저장한다. 이를 사용함으로써 기존 방식 대비약 37%의 ROM 크기만 필요하게 된다. 마지막으로이를 FPGA로 설계 및 제작하고 실험을 수행하였다.

#### References

- [1] D. A. Sunderland, R. A. Strauch, S. S. Wharfield, H. T. Peterson, and C. R. Cole, "CMOS/SOS frequency synthesizer LSI circuit for spread spectrum communications," *IEEE JSSC*, vol. 19, no. 4, pp. 497-506, Aug. 1984.

- [2] H. T. Nicholas, H. Samueli, and B. Kim, "The optimization of direct digital frequency synthesizer performance in the presence of finite word length effects," in 42nd Auun. Frequency Control Symp., pp. 356-363, 1988.

- [3] V. F. Kroupa, *Direct Digital Frequency Synthesizers*, New York: IEEE Press, 1999.

- [4] B.-D. Yang, J.-H. Choi, S.-H. Han, L.-S. Kim, and H.-K. Yu, "An 800-MHz low-power direct digital frequency synthesizer with an on-chip D/A converter," *IEEE J. Solid-State Circuits*, vol. 39, no. 5, pp. 761-774, May 2004.

- [5] A. Madisetti, A. Y. Kwentus, and A. N. Wilson, "A 100MHz, 16-b direct digital frequency synthesizer with a 100dBc spurious free dynamic range," *IEEE J. Solid State Circuits*, vol. 34, no. 8, pp. 1034-1043, Aug. 1999.